复旦大学集成电路设计:可编程ASIC器件详解与Xilinx、Altera比较

需积分: 10 116 浏览量

更新于2024-07-09

收藏 2.1MB PDF 举报

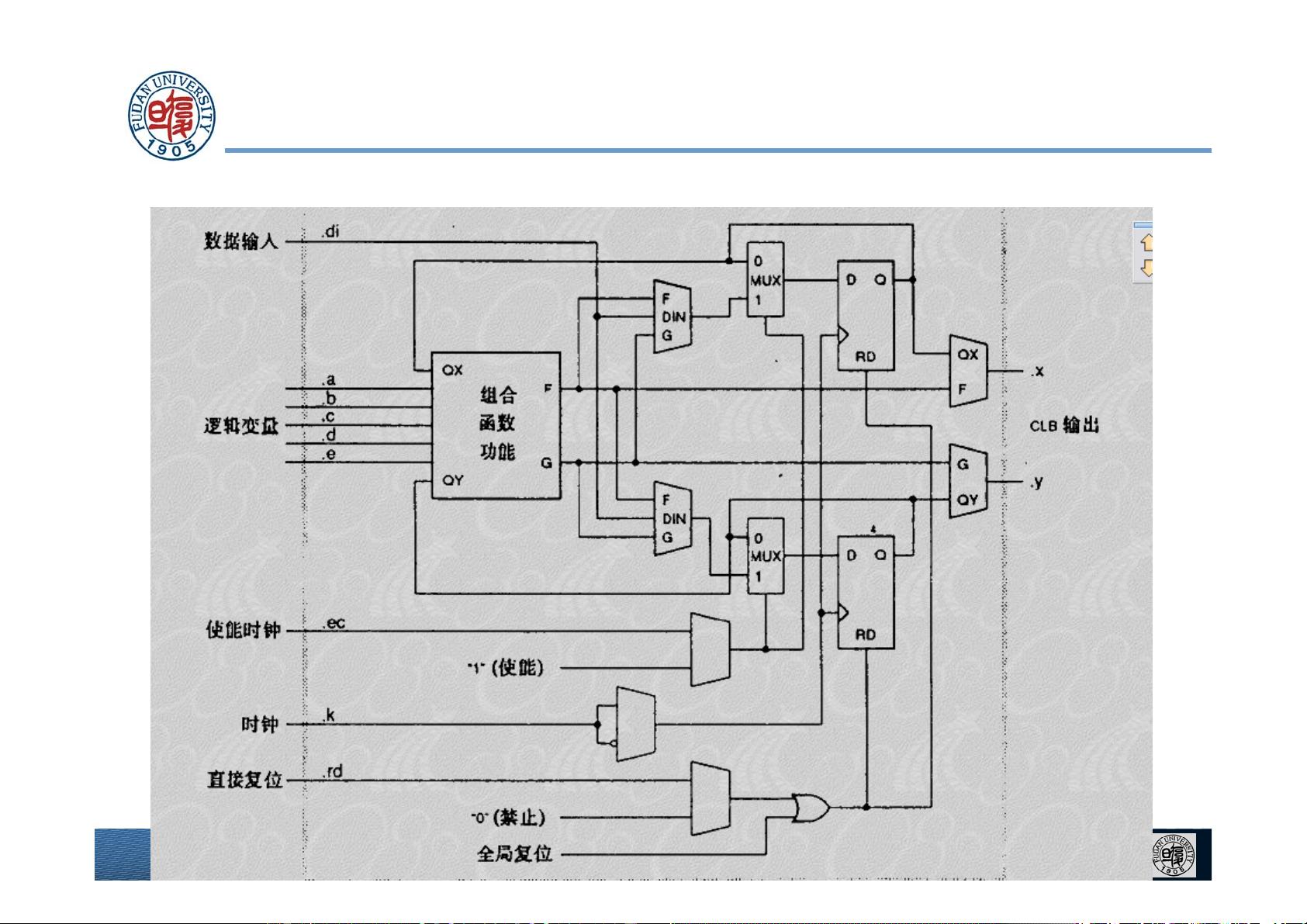

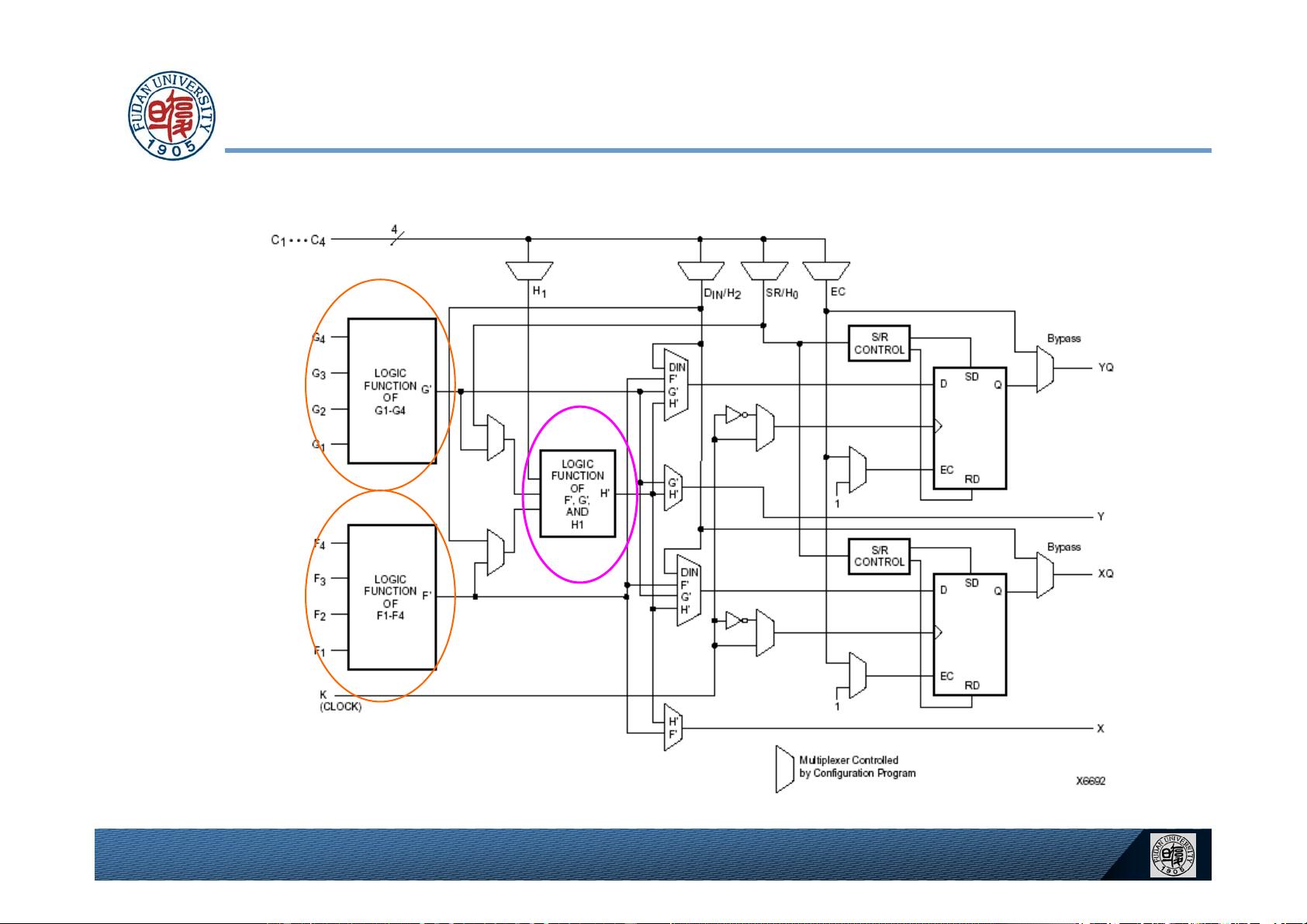

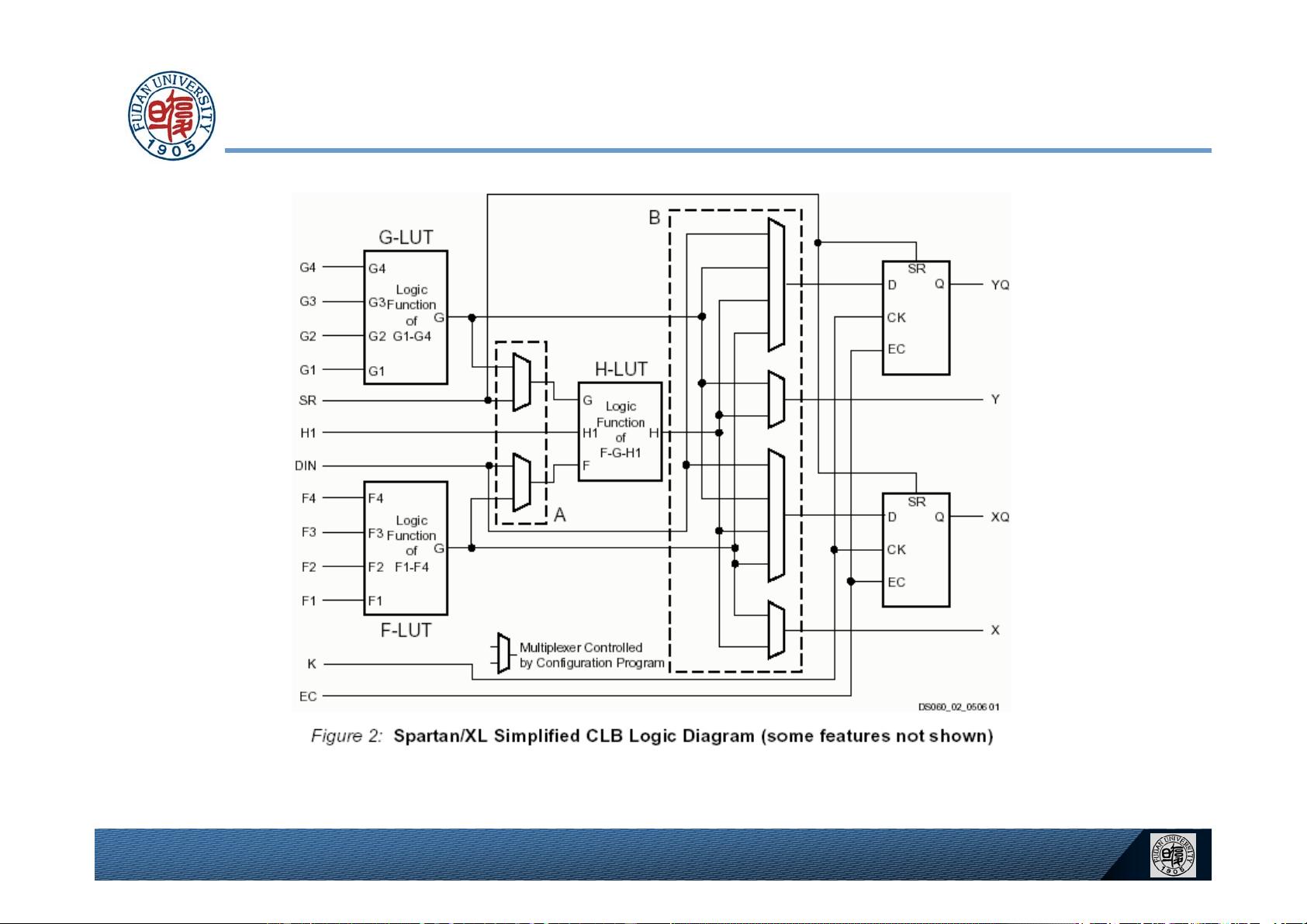

复旦大学的集成电路设计导论课程深入讲解了可编程ASIC(Application-Specific Integrated Circuit)器件,这是定制化电子设计的重要组成部分。在第三节课的第一部分中,教学内容围绕芯片的整体结构展开,包括其三大编程资源:可编程逻辑功能块(CLB)、可编程输入输出块和可编程连线资源。CLB是核心单元,用于实现用户自定义的逻辑功能;而可编程I/O块则负责与外部接口的交互,提供灵活的输入输出控制;连线资源则允许设计者根据需要配置芯片内部的连接。

Xilinx的Spartan-II系列是讨论的重点,它的内部结构包括一个延迟锁定环(DLL),用于提供高质量的高速时钟,减少失真,同时配备4kbit RAM块,有助于处理复杂的逻辑设计并提高系统的运行速度。通过减少与外部系统接口的需求,Spartan-II能够优化性能。

另一家厂商Altera的CPLD(Complex Programmable Logic Device)如MAX7000,其设计特点是一组16个宏单元组成的逻辑阵列块(LAB),以及可遍历连线阵列PIA,使得信号可以灵活地在不同宏单元之间传输。而Altera的FLEX10K芯片则展示了嵌入式阵列块EAB的特点,这些EAB集成了输入输出端口,提供高度定制化的I/O功能。

这些可编程ASIC器件的优势在于它们提供了高度灵活性,允许设计师根据项目需求进行定制,而不必像传统ASIC那样从头设计整个芯片。通过理解这些核心概念和技术,学生能够掌握ASIC设计的基本原理,并在实际项目中应用这些知识。学习这个主题对于希望进入硬件设计领域或者深入了解芯片级集成技术的学生来说,至关重要。

2021-05-20 上传

2021-05-12 上传

2021-05-21 上传

点击了解资源详情

点击了解资源详情

weixin_38613330

- 粉丝: 5

- 资源: 950

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜