克服空翻:边沿触发器与主从触发器解析

版权申诉

2 浏览量

更新于2024-07-17

收藏 552KB PPT 举报

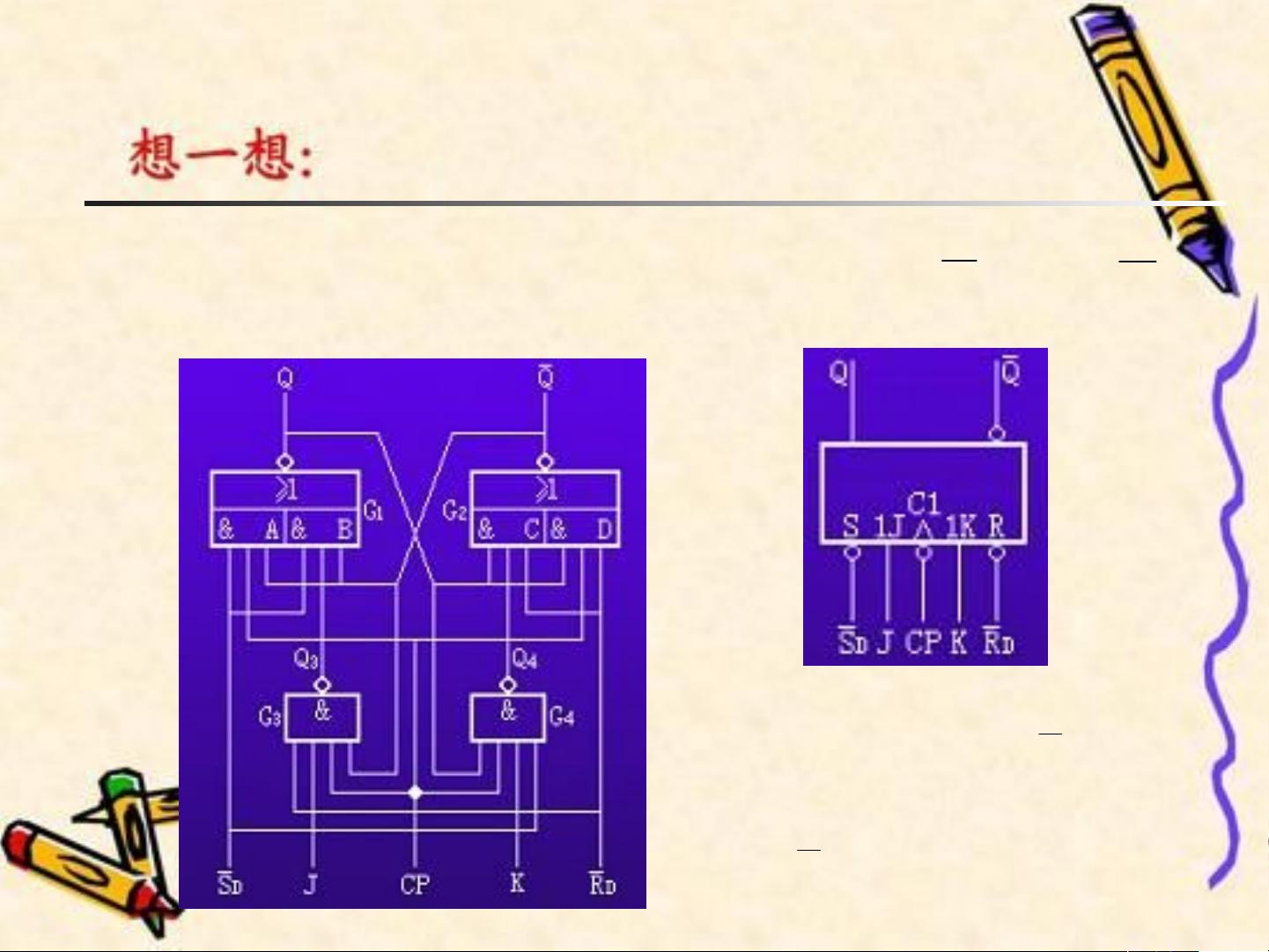

"该资源是一份关于第十三讲边沿触发器及其功能变换的PPT文档,主要探讨了数字逻辑电路中的边沿触发器概念,包括主从触发器,以及如何克服时序电路中的空翻问题。课程内容涵盖边沿触发器的种类,如D、JK、T和T'触发器的逻辑功能,以及如何通过手册了解MSI触发器的性能。重点在于理解触发器的逻辑功能和触发方式,掌握特性方程和驱动表。课堂讨论涉及D触发器的特性,复习了时序电路的基本概念,并指出在学习集成触发器时主要关注应用,而非内部电路细节。"

在数字逻辑电路中,边沿触发器是一种重要的时序电路组件,它的设计目的是解决同步触发方式中可能出现的“空翻”问题,提高电路的稳定性和抗干扰能力。空翻是指在时钟脉冲作用下,电路状态瞬间反复变化的现象,这会影响电路的正确工作。边沿触发器通过只在时钟脉冲的上升沿或下降沿响应输入信号,确保电路状态只在特定时刻改变,从而避免了空翻。

本讲中,边沿触发器的种类包括维持阻塞D触发器、边沿JK触发器以及CMOS边沿触发器等。以TTL边沿JK触发器为例,其逻辑符号中的“^”标记指示边沿触发输入,小圆圈表示下降沿触发,无圆圈则表示上升沿触发。TTL边沿JK触发器的逻辑功能可以用状态转移方程表示,如Qn+1 = JQ'n + K'Qn,其中Qn+1表示时钟脉冲后的状态,J和K分别为输入控制信号。

课程强调了理解触发器逻辑功能的重要性,如RS、D、JK、T、T'触发器的特性,以及如何利用手册查询MSI(中规模集成电路)触发器的逻辑功能和性能参数。同时,特性方程和驱动表是掌握触发器工作特性的关键,它们描述了触发器在不同输入条件下的状态转换。

课堂讨论部分提出了一个问题,即D触发器的特性方程中没有出现现态Qn,但尽管如此,D触发器仍然属于时序电路,因为它依赖于上一状态来确定下一状态,只是这个依赖关系在特性方程中并不直接体现。

本讲旨在深化对边沿触发器的理解,特别是其在克服空翻问题中的作用,以及如何利用这些触发器实现不同的逻辑功能。在实际应用中,了解触发器的外部行为和性能参数比深入研究其内部电路更为重要。

2008-11-26 上传

2009-06-17 上传

2021-09-19 上传

2021-09-18 上传

2021-09-20 上传

2010-11-22 上传

2022-05-08 上传

Dambulla

- 粉丝: 7

- 资源: 3万+

最新资源

- 通信基础知识.pdf

- 资源库管理系统用户手册

- android开发环境配置

- Spring+xFire实现webService

- svn结成eclipse详细配置

- visualbasicscript函数介绍

- c语言结构体讲解,TXT格式,适用于初学者,本人也是从网上搜索得到

- 图形学习题(有关图形学考试的)

- makefile书籍

- 如何让你的电脑定时开机

- 图像处理,matlab程序,retinex_frankle_mccann算法加直方图均衡化算法,去雾

- tomcat下配置jsp.doc

- PLSQL常用方法汇总.doc

- vhdl课程设计密码锁 vhdl课程设计密码锁

- Oracle 安装图解.doc

- 最小生成树总结acm竞赛