优化时钟电路设计:信号完整性和参数优化

需积分: 9 86 浏览量

更新于2024-09-07

1

收藏 320KB PDF 举报

"本文详细介绍了如何设计最优化的时钟电路,重点关注高速数字电路中的信号完整性问题,特别是针对49FCT3807与SDRAM的一驱一和一驱二时钟电路进行了深入的SI分析和参数优化。"

在高速数字电路设计中,时钟电路的优化至关重要,因为它不仅关乎数据的准确传输,还直接影响系统的稳定性和可靠性。设计人员需要关注模拟电路领域内的传输线效应,这些效应可能导致系统故障。通过49FCT3807与SDRAM时钟电路的例子,文章揭示了硬件和PCB设计工程师在设计过程中应注意的关键点。

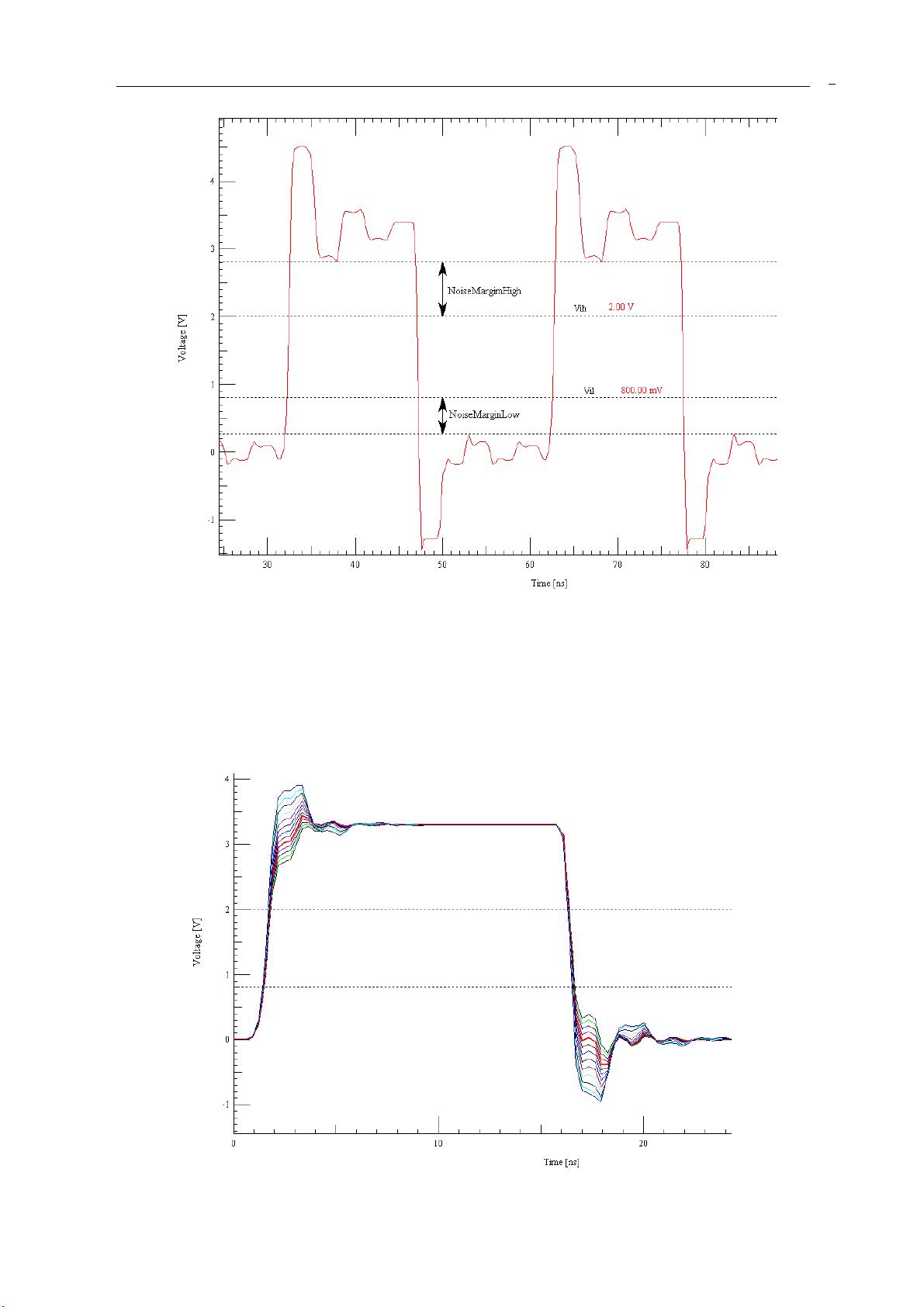

首先,对于一驱一时钟电路(49FCT3807-SDRAM),文章提到了网络拓扑的设计。由于3807的低输出阻抗(约6-10欧姆),时钟网络的特征阻抗通常设计为50欧姆。为了减少反射,应在3807的输出端添加防反射串联电阻。图2显示了加串阻与不加串阻时的波形差异,加串阻能有效降低反射电压,减小振铃现象,从而提高噪声裕度。

噪声裕度是衡量信号质量的重要指标,包括NoiseMarginHigh和NoiseMarginLow,前者表示“1”电平的最低电压与阈值Vih之间的差值,后者是“0”电平阈值Vil与最高电压之间的差值。设计最优化的时钟电路应确保足够的噪声裕度以保证信号的正确识别。

在选择串联电阻的阻值时,文章进行了详细分析。通过扫描22至58欧姆范围内的电阻值,发现最佳值为46欧姆,实际应用中可选用43至49.9欧姆的电阻,允许±5%的公差。这个最佳值取决于驱动器的特性以及印制线的特征阻抗。

此外,文章还讨论了驱动器与串阻之间线长对噪声裕度的影响。当总线长度固定为3500微米时,不同的线长会改变噪声裕度,设计者需根据具体应用场景调整线长以达到最佳性能。

设计最优化的时钟电路需要综合考虑驱动器特性、印制线设计、噪声裕度和信号反射等因素。在进行高速数字电路设计时,理解并应用这些概念至关重要,这有助于预防和解决信号完整性问题,从而确保系统运行的高效和稳定。同时,获取准确的器件模型如IBIS和Spice模型也是确保设计精度的重要步骤。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-26 上传

2024-06-26 上传

2021-07-26 上传

2021-07-26 上传

2020-04-15 上传

2019-09-14 上传

weixin_39841856

- 粉丝: 491

- 资源: 1万+

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程