UCC29950

www.ti.com.cn

ZHCSDI3A –SEPTEMBER 2014–REVISED MARCH 2015

7 Detailed Description

7.1 Overview

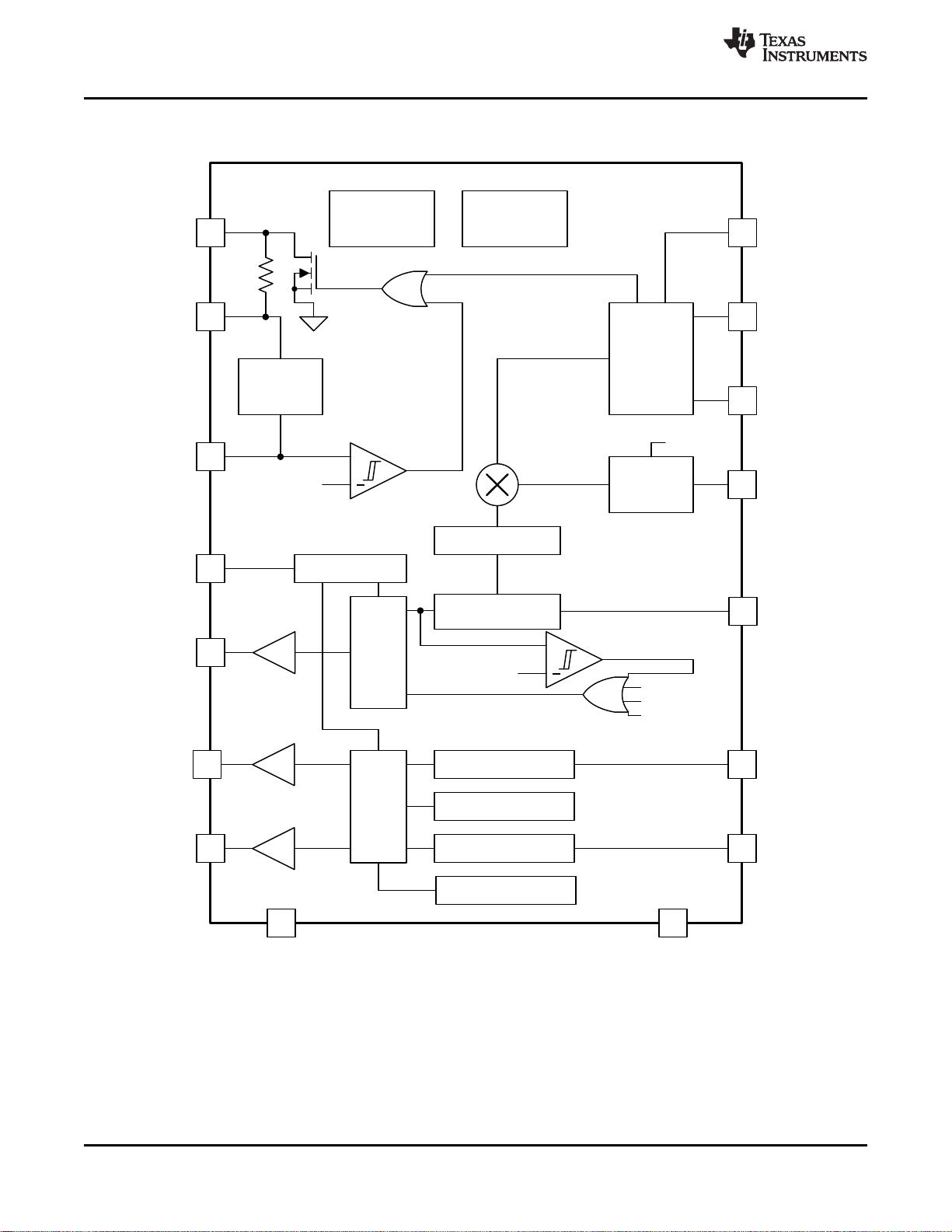

The UCC29950 combines all the functions necessary to control a Boost PFC and LLC power system. It is

packaged in an SOIC-16 package. The SUFG and SUFS pins allow the system designer to use an external

depletion mode MOSFET to provide start up power instead of using a dissipative resistor. The use of high-

impedance voltage sensing networks further reduces standby power. The combo device uses information from

both PFC and LLC stages to optimize the system efficiency, transient response and standby power. The

controller can be operated with bias current supplied from a small external PSU (Aux Bias) or from a winding on

the LLC transformer (Self Bias). In Aux Bias Mode, the MD_SEL/PS_ON pin allows the user to turn on the PFC

stage alone or both PFC and LLC stages.

The UCC29950 has many protection features, these include:

• Bias Rail Under-Voltage Lockout

• Active X-Cap Discharge

• Line Under-Voltage Detection

• Line Over-Voltage Detection

• Line Brownout Detection

• Three Level Output Overcurrent Profile on LLC Stage

• PFC Stage Constant Input Power Limit

• PFC Stage Input Current Limit

• PFC Stage Second Current Limit

• PFC Stage Output Overvoltage Protection

• V

BLK

Sensing Network Fault Detection

• V

BLK

Over-Voltage Protection

• PFC and LLC Stage Soft-Start

• PFC Stage Frequency Dithering

• Thermal Shutdown

The UCC29950 implements an advanced control algorithm to control the PFC stage input current. This

proprietary hybrid method combines both average and peak-mode control methods.

• Accurate control of the average current drawn from the line gives good THD.

• Peak inductor current information is used to terminate each PFC switching cycle.

• The algorithm is insensitive to variations in the peak-to-average current ratio.

The input current is accurately controlled so that it follows the correct sinusoidal shape and also gives inherent

cycle-by-cycle protection against excess MOSFET current. A further advantage is that the control loop is

insensitive to PFC inductor and bulk capacitor variations. The UCC29950 takes full advantage of this fact to

implement internal compensation of the PFC stage. This simplifies the system designer’s task and reduces the

external component count. A sophisticated soft-start algorithm is used to achieve a constant soft-start ramp time

over a wide range of bulk capacitor values and initial conditions.

An LLC stage is typically used to convert the PFC stage output to an isolated final voltage for system use. The

UCC29950 provides all the primary-side functions needed to control such a second stage. The input to the FB

pin is an isolated control signal from the output. This signal is fed into a voltage-to-frequency converter (VCO).

The VCO inserts an appropriate dead time and the resulting signals are routed through some on-chip drivers

connected to the GD1 and GD2 outputs. The dead time is shortest at low LLC frequencies and is increased

automatically as frequency is increased. A three level Over-Current Protection (OCP) function stops the GD1 and

GD2 signals if the current signal at the LLC_CS pin goes outside of a defined current vs time profile.

Copyright © 2014–2015, Texas Instruments Incorporated 13