TI的TDA4VE TDA4AL TDA4VL Jacinto 7智能视觉处理器

版权申诉

61 浏览量

更新于2024-06-27

收藏 4.89MB PDF 举报

"DA4VE TDA4AL TDA4VL Jacinto Processors, Silicon Revision 1.0.pdf"

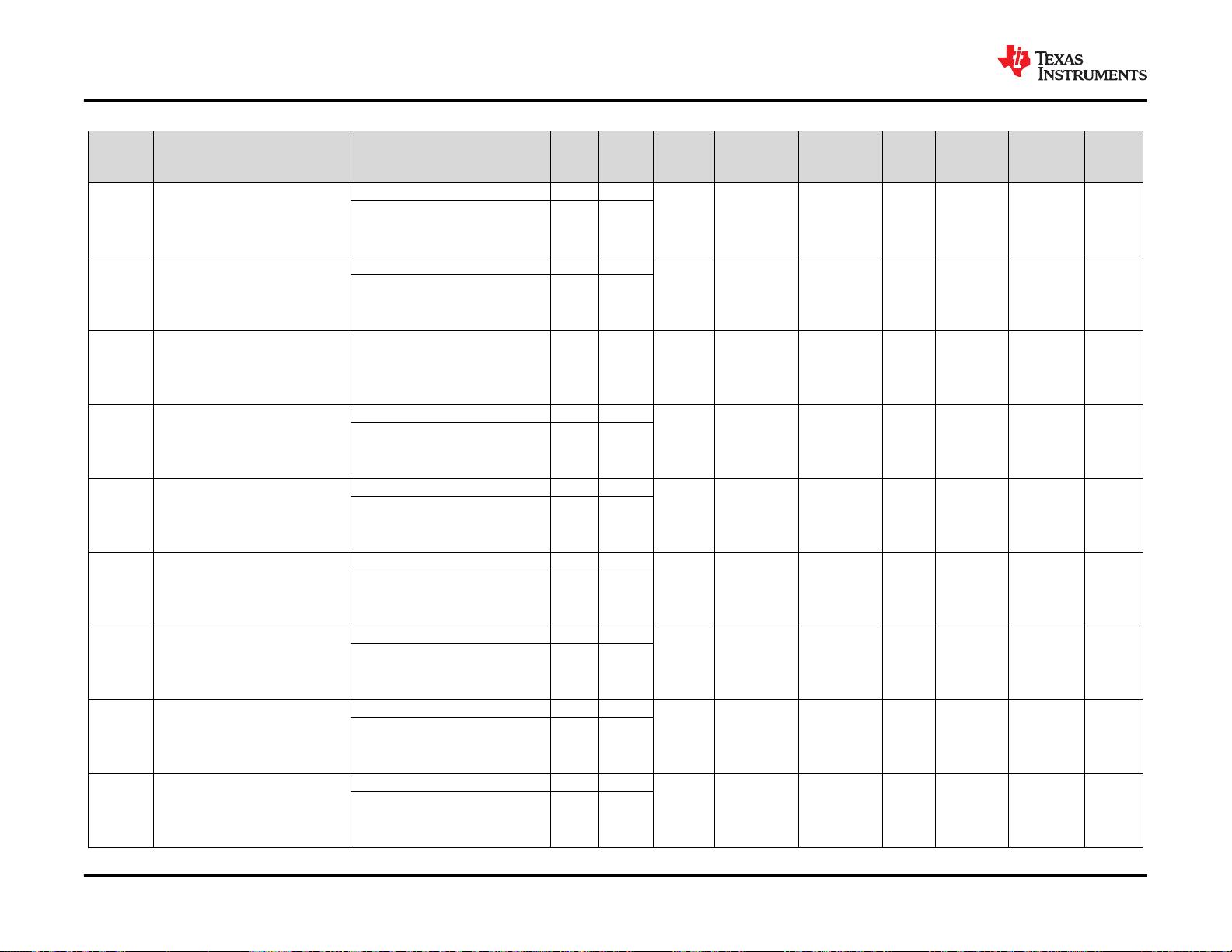

TI的DA4VE、TDA4AL和TDA4VL处理器家族是基于进化型的Jacinto 7架构设计的,主要针对智能视觉相机应用。这些处理器利用了TI在视觉处理器市场超过十年的领导地位所积累的丰富市场知识。该系列处理器旨在提供高能效的传统算法和深度学习算法计算能力,具有业界领先的能效比,并通过高度系统集成来实现可扩展性和降低成本,以满足高级视觉应用的需求。

1. 处理器核心特性:

- C7x浮点向量DSP:包含两个核心,频率高达1.0GHz,提供160GFLOPS(每秒浮点运算次数)和512GOPS(每秒操作数)的高性能。

- 深度学习矩阵乘法加速器(MMA):最高可达8TOPS(8位)的运算能力,在1.0GHz时运行。

- 视觉处理加速器(VPAC):集成了图像信号处理器(ISP)和多个视觉辅助加速器,用于高效处理视觉数据。

- 深度和运动处理加速器(DMPAC):专门用于处理深度感知和运动计算任务。

- 双核64位Arm Cortex-A72微处理器子系统:频率可达2GHz,每个双核Cortex-A72集群有1MB共享L2缓存,每个Cortex-A72核心有32KB L1数据缓存和48KB L1指令缓存。

2. 实时控制单元:

- 最多六个Arm Cortex-R5F MCU,频率可达1.0GHz,每个具有16KB I-Cache、16KB D-Cache和64KB L2 TCM。

- 两个隔离的MCU子系统中的Arm Cortex-R5F MCU,确保安全性和独立性。

- 四个(DA4VE)或两个(TDA4AL/TDA4VL)Cortex-R5F MCU用于通用计算分区。

3. GPU配置:

- 图形处理单元(GPU)采用IMGBXS-64-4,配备256KB缓存,频率可达800MHz,提供50GFLOPS性能和4GTexels/s的纹理处理速度(DA4VE和TDA4VL)。

4. 内存子系统:

- 集成高达4MB的片上L3 RAM,支持ECC错误保护和一致性。

- ECC(错误校验码)确保数据完整性。

- 共享一致性缓存,支持多核间的高效通信。

- 支持外部内存接口,如DDR4和LPDDR4X,以及各种其他外设连接。

这些处理器的设计考虑了智能视觉应用的复杂需求,包括自动驾驶、工业自动化、监控和安全等领域。强大的硬件加速器和高效的内存架构使得它们能够在处理图像处理、计算机视觉和深度学习任务时表现出色,同时保持低功耗,从而成为智能视觉解决方案的理想选择。

2018-05-02 上传

2021-09-25 上传

2024-11-08 上传

2023-05-04 上传

2024-11-08 上传

2024-11-08 上传

2023-10-10 上传

2024-07-18 上传

智驾

- 粉丝: 2538

- 资源: 60

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新