Cadence版图设计与验证教程:清华微电子所讲义

需积分: 15 120 浏览量

更新于2024-07-24

2

收藏 4MB PPT 举报

"cadence_版图讲义_清华微电子所_"

这是一份由清华大学微电子研究所编写的关于Cadence版图设计的讲义,适用于初学者。Cadence是电子设计自动化(EDA)领域中的一款重要软件,广泛应用于集成电路(IC)设计,特别是版图设计和验证。

1. Cadence设计系统介绍:

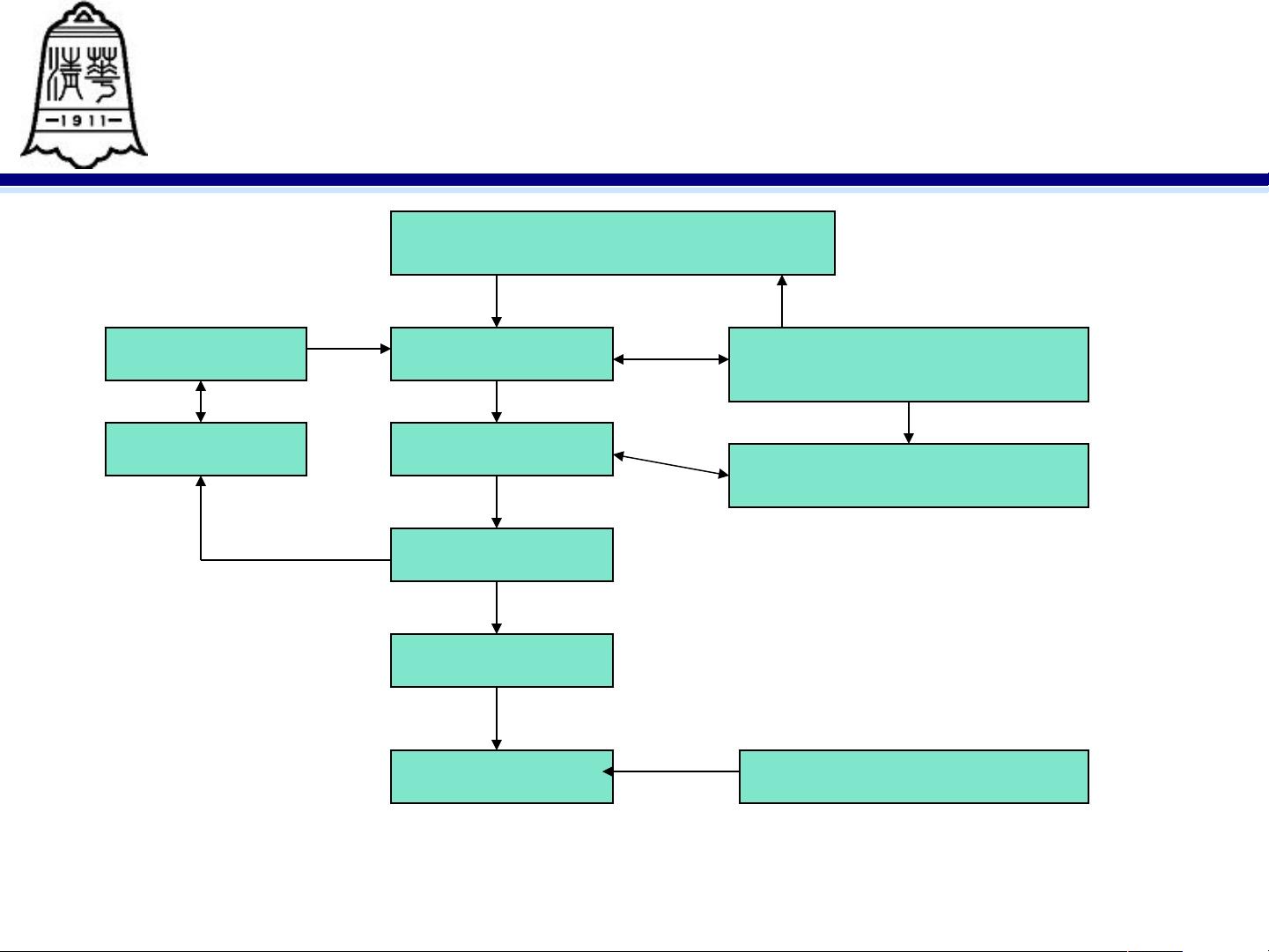

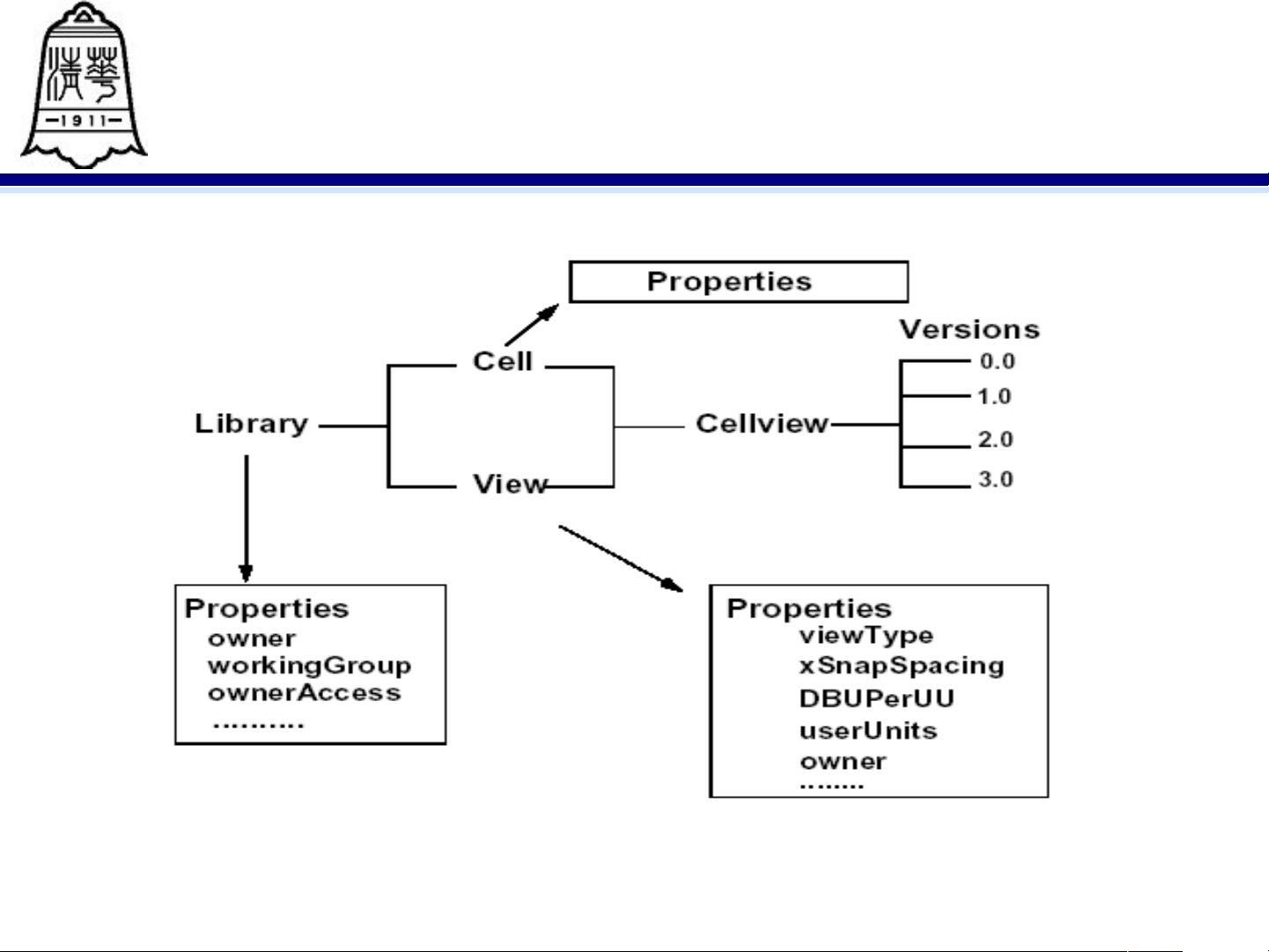

Cadence设计系统是一款全面的集成电路设计平台,它涵盖了从电路设计、逻辑综合、仿真验证到物理实现等多个阶段。系统概述中包括了设计流程的介绍,如前端设计、后端布局布线等,以及系统组织结构的解析,帮助用户理解如何启动和操作该软件。

2. 版图设计工具-Virtuoso LE:

Virtuoso Layout Editor(Virtuoso LE)是Cadence提供的一款高级版图编辑器,用于实现物理设计的细节布局和布线。它具有丰富的图形界面和强大的编辑功能,支持多层布局,可以处理复杂的半导体工艺节点下的版图设计。

3. 版图验证工具-Diva & Dracula:

- Diva(Design Integrity Verification Assistant)是一款强大的版图验证工具,用于检查版图的电气规则错误(ERC)和设计规则检查(DRC),确保版图符合制造工艺要求。

- Dracula是另一个用于版图验证的工具,它专注于寄生参数提取,可以帮助设计师分析版图的 parasitic effects,这些效应在高速电路设计中尤为重要。

4. Cadence学习的重要性:

随着集成电路发展趋势的不断推进,特征尺寸不断缩小,电源电压降低,晶体管数量急剧增加,这使得设计的复杂度大幅提升。为了应对这些挑战,掌握像Cadence这样的强大EDA工具变得至关重要。讲义中列举了从1997年至2012年的集成电路发展趋势,展示了工艺技术进步对设计复杂度的影响。

5. 设计流程中的其他关键环节:

讲义还可能涉及VHDL仿真、行为综合、逻辑综合、可测性设计和低功耗设计等关键步骤。这些环节在IC设计中扮演着重要角色,VHDL用于描述硬件行为,而行为综合和逻辑综合则将高级设计语言转换为门级网表。可测性设计确保芯片在生产后的测试效率,低功耗设计则是在满足性能需求的同时,尽可能降低功耗。

这份"cadence_版图讲义_清华微电子所_"提供了全面的Cadence使用入门知识,覆盖了从设计流程、工具使用到实际问题解决的多个方面,对于想要进入集成电路设计领域的学习者来说,是一份非常宝贵的参考资料。

2010-05-28 上传

2021-10-06 上传

2021-10-07 上传

2011-08-08 上传

2011-03-17 上传

2021-10-06 上传

2021-10-06 上传

2011-04-27 上传

2021-10-06 上传

lzhzhup

- 粉丝: 1

- 资源: 3

最新资源

- 平尾装配工作平台运输支撑系统设计与应用

- MAX-MIN Ant System:用MATLAB解决旅行商问题

- Flutter状态管理新秀:sealed_flutter_bloc包整合seal_unions

- Pong²开源游戏:双人对战图形化的经典竞技体验

- jQuery spriteAnimator插件:创建精灵动画的利器

- 广播媒体对象传输方法与设备的技术分析

- MATLAB HDF5数据提取工具:深层结构化数据处理

- 适用于arm64的Valgrind交叉编译包发布

- 基于canvas和Java后端的小程序“飞翔的小鸟”完整示例

- 全面升级STM32F7 Discovery LCD BSP驱动程序

- React Router v4 入门教程与示例代码解析

- 下载OpenCV各版本安装包,全面覆盖2.4至4.5

- 手写笔画分割技术的新突破:智能分割方法与装置

- 基于Koplowitz & Bruckstein算法的MATLAB周长估计方法

- Modbus4j-3.0.3版本免费下载指南

- PoqetPresenter:Sharp Zaurus上的开源OpenOffice演示查看器