VHDL实现FIR滤波器:15阶低通滤波器设计

"该资源是一份关于使用VHDL语言设计FIR滤波器的期末大作业,作者曹振翔,指导教师黎海涛,完成于2015年12月19日。作业包括两个部分:由VHDL实现的BPSK解调和15阶FIR低通滤波器设计。"

正文:

在电子工程领域,可编程逻辑电路(PLC)是实现数字系统设计的关键技术之一。VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛用于数字系统的建模、设计和验证。本作业主要探讨了如何利用VHDL语言设计和实现两种重要的数字信号处理组件:BPSK解调器和FIR(Finite Impulse Response)滤波器。

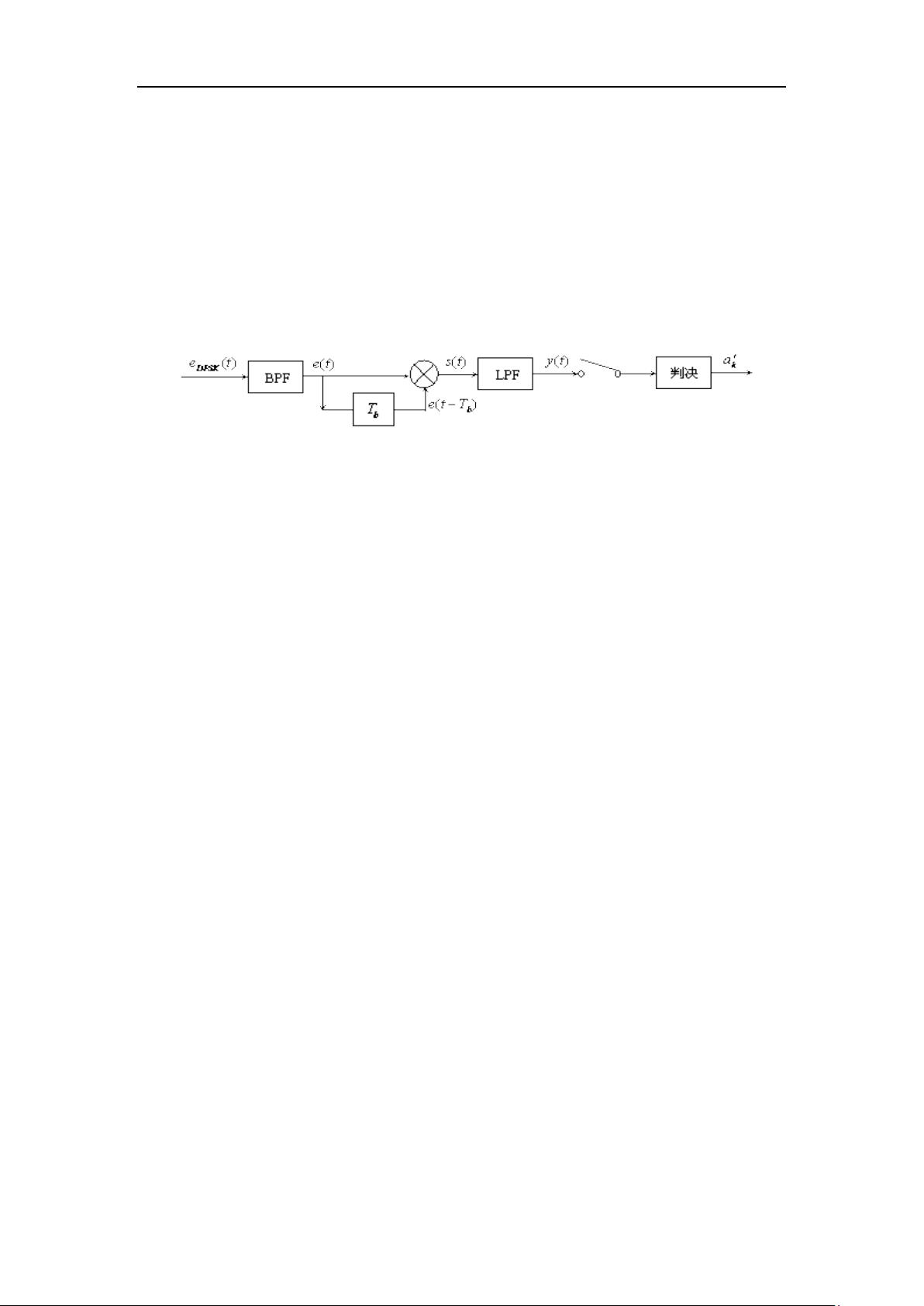

实验一基于VHDL的BPSK解调,BPSK(Binary Phase Shift Keying)是一种常见的数字调制方式,其信息被编码在载波相位的两个状态之间切换。在解调过程中,由于BPSK信号的幅度恒定且无法通过频率分离,所以通常采用相干解调方法。在VHDL程序实现中,通常会涉及分频计数器、相位比较器等模块,通过检测载波相位的变化来恢复原始的基带信号。

实验二则聚焦于15阶FIR低通滤波器的设计。FIR滤波器因其线性相位特性、可调整的滤波响应以及易于硬件实现而广泛应用于通信和信号处理。15阶FIR滤波器意味着它包含了15个延迟单元,可以提供一定的频率选择性。设计FIR滤波器通常包括以下几个步骤:

1. 实验原理与思路:首先,理解FIR滤波器的结构,其基本单元是延迟线和加法器,通过线性组合不同延迟的输入样本来形成输出。设计思路可能包括确定滤波器的性能指标(如截止频率、阻带衰减等),然后在MATLAB等工具中进行参数设定。

2. 实验过程:在MATLAB中,可以使用滤波器设计函数(如`fir1`)生成滤波器系数,这些系数将用于VHDL代码中。VHDL设计包括以下部分:

- 延迟单元(Delay Unit):用于存储输入信号的一个或多个采样周期。

- 加法器(Adder):将延迟单元中的样点与权值相乘后相加,形成滤波器的输出。

- 乘法器(Multiplier):对每个延迟样本与对应的滤波器系数进行乘法操作。

- 减法器(Subtractor):在某些特定设计中,可能会用到减法器来实现特殊的滤波效果。

3. 仿真结果与分析:设计完成后,使用硬件描述语言编译器进行综合,并在硬件模拟器中进行功能和时序仿真,验证滤波器是否满足设计规格。最后,根据仿真结果进行性能分析,包括频率响应、失真度和信噪比等方面的评估。

4. 心得体会:这部分可能包含了作者在设计过程中遇到的问题、解决策略以及对VHDL语言和FIR滤波器设计更深入的理解。

这份作业详细展示了如何使用VHDL语言进行数字信号处理系统的实现,对于理解FIR滤波器的工作原理和VHDL编程技巧具有重要的学习价值。

2024-02-02 上传

2023-10-11 上传

2023-07-09 上传

2023-07-27 上传

2023-05-31 上传

2023-04-28 上传

魂爵

- 粉丝: 3

- 资源: 7

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性