高速数字设计:电源分布与信号完整性详解

需积分: 10 200 浏览量

更新于2024-07-23

收藏 182KB PDF 举报

高速数字设计和信号完整性分析是一门关键的领域,它关注在高速数字电路设计过程中如何确保信号质量与系统性能。信号完整性主要涉及到电源分布系统的设计,这是电子设计中的基础组成部分,旨在为高速数字电路提供稳定、低噪声的供电环境。

电源分布系统(PDS)的基本概念强调了电源层和地层之间的有效去耦对于信号传输的重要性。在多层板的叠层结构中,通过足够的去耦电容,交流信号能够轻松穿越各层,形成一个低阻抗的平面,使得电流回路更加高效。设计目标包括为数字信号提供恒定的电压参考,确保逻辑电路的正常工作,这包括提供低阻抗的电源和地连接,以及减少公共通路阻抗带来的电源和地电位差。

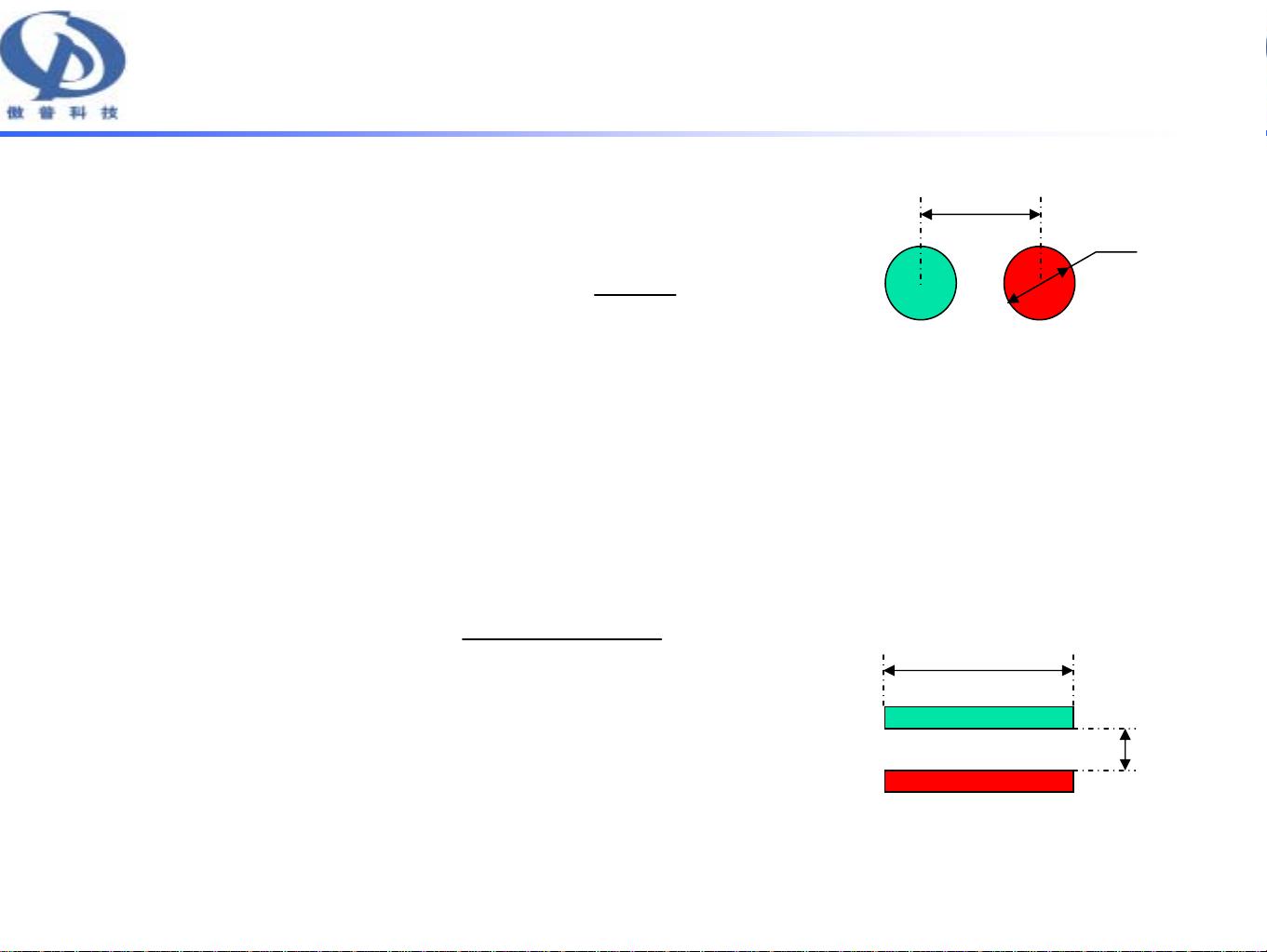

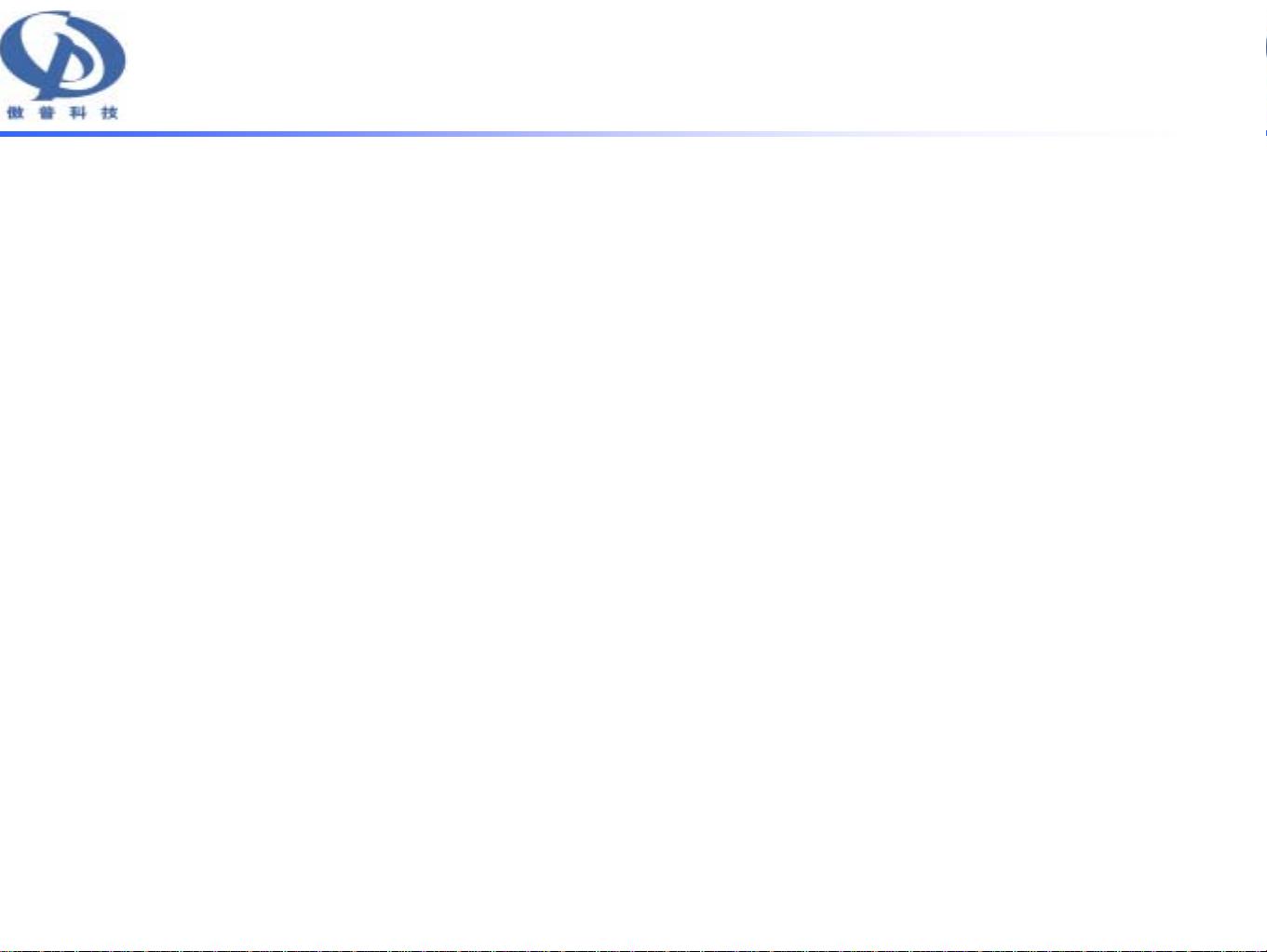

PDS的阻抗与其所需电流成反比,与电源电压的波动允许范围成正比。寄生电阻(ESR)在直流或低频时影响电源电压稳定性,而寄生电感(ESL)在高频情况下则因交流电流产生的电压差显著。为了减小这些影响,设计者需考虑电源线的长度、间距和线径,例如,平行线的电感可以通过特定公式计算,而对于多层扁平带状电源线,考虑线长、间距和层数等因素也有助于优化。

一般设计规则包括确保PDS的稳定性和无噪声,这意味着在设计时需要遵循一系列最佳实践,如选择合适的去耦电容布局、控制线宽和间距,以及采用有效的接地策略。这些都是为了防止信号反射、串扰和噪声引入,从而提高整个系统的信号质量和可靠性。

在高速数字设计中,信号完整性分析至关重要,因为它直接影响到信号的传输速度、时序准确性和数据完整性。理解并遵循这些基本原则和设计方法,可以帮助工程师在实际项目中构建出高效且健壮的高速数字电路系统。

395 浏览量

448 浏览量

188 浏览量

229 浏览量

118 浏览量

点击了解资源详情

120 浏览量

点击了解资源详情

229 浏览量

drkshcn

- 粉丝: 1

最新资源

- 网页自动刷新工具 v1.1 - 自定义时间间隔与关机

- pt-1.4协程源码深度解析

- EP4CE6E22C8芯片三相正弦波发生器设计与实现

- 高效处理超大XML文件的查看工具介绍

- 64K极限挑战:国际程序设计大赛优秀3D作品展

- ENVI软件全面应用教程指南

- 学生档案管理系统设计与开发

- 网络伪书:社区驱动的在线音乐制图平台

- Lettuce 5.0.3中文API文档完整包下载指南

- 雅虎通Yahoo! Messenger v0.8.115即时聊天功能详解

- 将Android手机转变为IP监控摄像机

- PLSQL入门教程:变量声明与程序交互

- 掌握.NET三层架构:实例学习与源码解析

- WPF中Devexpress GridControl分组功能实例分析

- H3Viewer: VS2010专用高效帮助文档查看工具

- STM32CubeMX LED与按键初始化及外部中断处理教程