Verilog设计详解:层次结构、模块关系与测试示例

版权申诉

198 浏览量

更新于2024-07-03

收藏 245KB PPT 举报

Verilog是一种高级硬件描述语言(HDL),它被广泛用于数字逻辑电路的设计与实现,特别是在硬件工程师和嵌入式系统开发人员中。这份文档名为"Verilog设计举例.ppt",主要通过实例来介绍如何使用Verilog进行层次化的结构模块设计,以及不同模块类型之间的关系管理,同时强调了测试和验证在设计过程中的关键作用。

首先,文档的核心内容是围绕结构模块的层次化组织展开的。层次化设计有助于提高代码的可读性和复用性,将复杂的逻辑功能分解为小的、独立的模块,如用门级结构描述的D触发器。D触发器是一种双稳态存储器,它基于输入数据(d)和时钟(clk)来决定下一个状态。设计中涉及了多个基本门级结构,如NAND和NOT,这些都被用来构建触发器的不同部分,如数据输入端data、清零端clear、输出端q和qb。

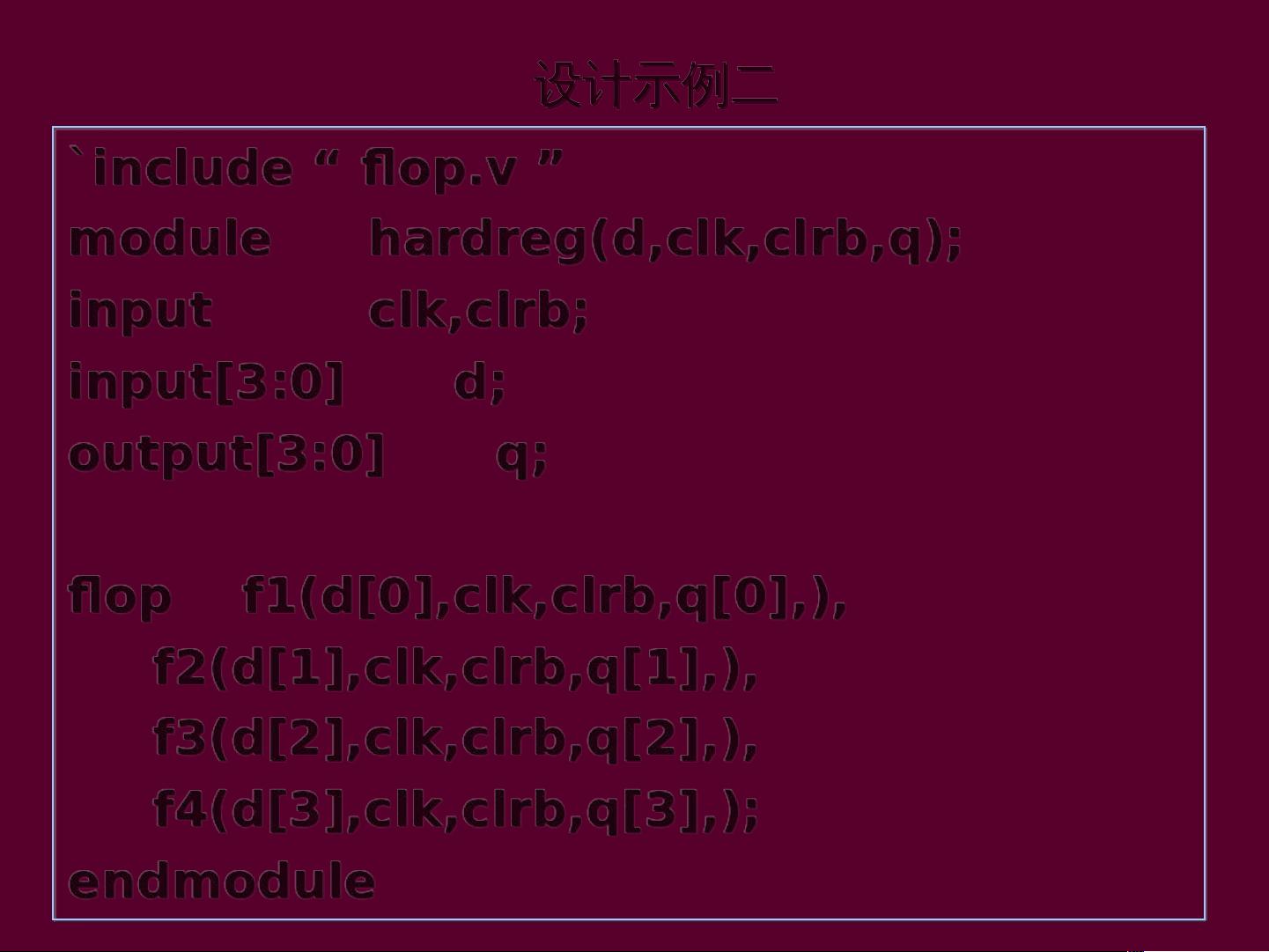

设计示例一详细展示了如何使用这些基本模块构造一个完整的Flop,即D触发器。Flop模块接收data、clock和clear信号作为输入,产生新的状态q和更新后的状态qb。在这个模块中,每个逻辑操作都有明确的时间延迟,例如#10和#9分别表示操作时间。此外,还有初始化寄存器(iv1和iv2)来设置初始条件,确保电路在正确的时间点启动。

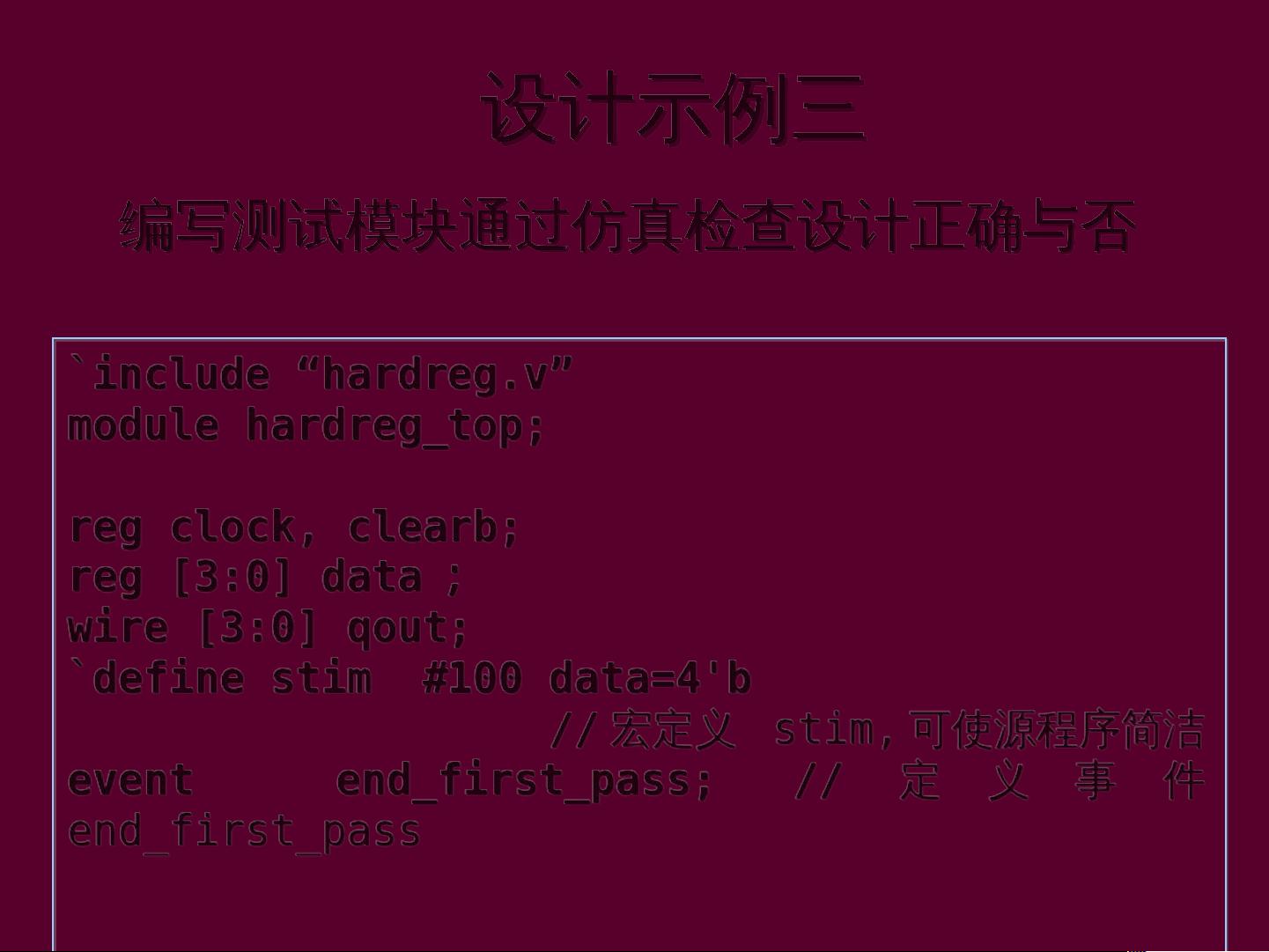

文档还强调了模块间的连接关系,如NAND门的连接、数据流和控制信号的传递。通过清晰地定义输入和输出,以及使用适当的控制逻辑,确保了模块间的正确交互。在设计过程中,测试和验证环节至关重要,因为它能够确保设计的正确性和一致性。iv1和iv2是示例中用来模拟测试输入的,通过这些测试用例来驱动模块并检查其行为是否符合预期。

总结来说,"Verilog设计举例.ppt"提供了实际的案例来教授如何运用Verilog语言进行数字电路设计,特别是层次化结构的搭建、不同模块之间的交互以及验证过程。这对于学习Verilog的初学者来说是一份宝贵的参考资料,可以帮助他们掌握硬件描述语言的关键技能。

2021-09-17 上传

2021-09-21 上传

2021-09-24 上传

2022-06-22 上传

2021-10-24 上传

2021-10-02 上传

点击了解资源详情

点击了解资源详情

智慧安全方案

- 粉丝: 3812

- 资源: 59万+

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜