没有合适的资源?快使用搜索试试~ 我知道了~

首页TI公司TMS320LF2407A DSP控制器详细规格解析

TI公司TMS320LF2407A DSP控制器详细规格解析

需积分: 11 9 下载量 182 浏览量

更新于2024-07-25

2

收藏 1.76MB PDF 举报

"TMS320LF2407A.PDF是TI(Texas Instruments)公司的一款数字信号处理器(DSP)的数据手册,涵盖了TMS320LF2407A以及与其相关的LF和LC系列芯片的详细信息。这些芯片基于TMS320C2xx DSP CPU核心,具有高性能、低功耗的静态CMOS技术特点。"

TMS320LF2407A是一款3.3伏低功耗设计的DSP控制器,其指令周期时间为25纳秒(40MHz时),能够提供40百万指令每秒(MIPS)的性能。该芯片与F243/F241/C242代码兼容,并且在指令集和模块上与F240兼容,这意味着开发者可以利用已有的软件资源进行开发。

LF系列(如LF2407A、LF2406A、LF2403A和LF2402A)和LC系列(如LC2406A、LC2404A、LC2403A和LC2402A)提供了Flash和ROM的设备选项。LF系列包含Flash或EEPROM存储器,而LC系列则包含ROM。其中,LF240xA设备内建有BootROM,支持SCI/SPI引导加载程序。

在内存方面,TMS320LF2407A拥有高达32K字x16位的Flash或ROM,以及最多2.5K字x16位的数据/程序RAM。此外,还包括544字的双访问RAM和最多2K字的单访问RAM。这些内存资源对于实时处理和数据存储至关重要。

该芯片还集成了两个事件管理器(EV模块,EVA和EVB),每个模块都包含两个16位通用定时器和八个16位脉宽调制(PWM)通道,可用于三相逆变器和其他控制应用。这样的硬件配置使得TMS320LF2407A非常适合于电机控制、电源转换和其它需要高效能信号处理的场合。

此外,TMS320LF2407A还提供了一个可编程的“代码安全”特性,用于保护内部Flash/ROM中的代码不被非法访问或篡改,确保了系统的安全性和可靠性。

TMS320LF2407A是一款针对工业应用设计的高性能、低功耗DSP,具备强大的处理能力、丰富的内存资源和灵活的外设接口,适合于需要复杂控制算法和实时性能的应用,如电机控制、自动化系统和能源管理等领域。

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145L − JULY 2000 − REVISED SEPTEMBER 2007

16

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

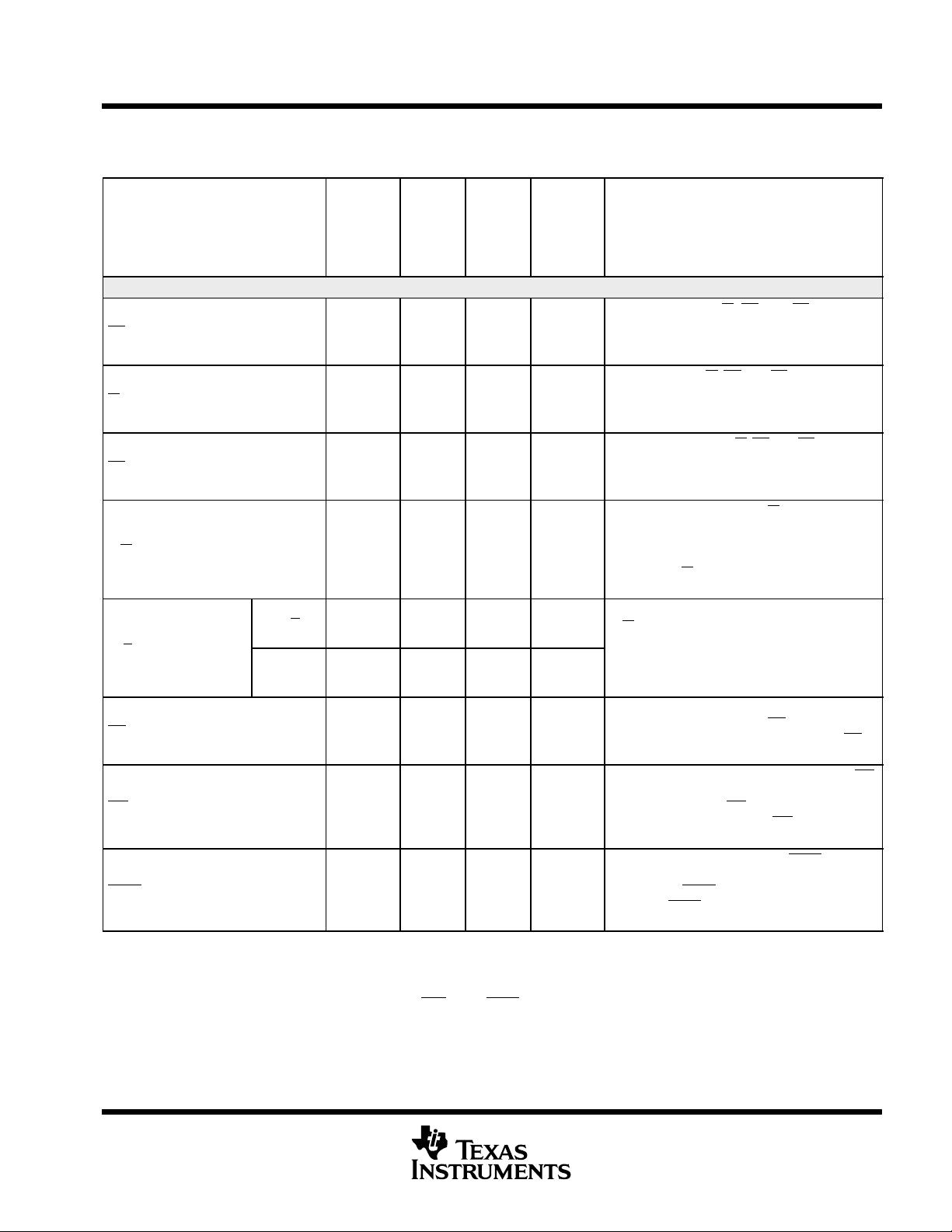

pin functions (continued)

Table 2. LF240xA and LC240xA Pin List and Package Options

†‡

(Continued)

PIN NAME

LF2407A

(144-PGE)

2406A

(100-PZ)

LC2404A

(100-PZ)

2403A,

LC2402A

(64-PAG)

and

2402A

(64-PG)

DESCRIPTION

EMULATION AND TEST (CONTINUED)

TDI 139 96 96 30

JTAG test data input (TDI) with internal pullup. TDI

is clocked into the selected register (instruction or

data) on a rising edge of TCK. (↑)

TDO 142 99 99 31

JTAG scan out, test data output (TDO). The

contents of the selected register (instruction or

data) is shifted out of TDO on the falling edge of

TCK. (↓)

TMS 144 100 100 32

JTAG test-mode select (TMS) with internal pullup.

This serial control input is clocked into the TAP

controller on the rising edge of TCK. (↑)

TMS2 36 25 25 48

JTAG test-mode select 2 (TMS2) with internal

pullup. This serial control input is clocked into the

TAP controller on the rising edge of TCK. Used for

test and emulation only. This pin can be left

unconnected in user applications. If the PLL bypass

mode is desired, TMS2, TMS, and TRST

should be

held low during reset. (↑)

TRST 1 1 1 33

JTAG test reset with internal pulldown. TRST, when

driven high, gives the scan system control of the

operations of the device. If this signal is not

connected or driven low, the device operates in its

functional mode, and the test reset signals are

ignored. (↓)

NOTE: Do not use pullup resistors on TRST

; it has

an internal pulldown device. TRST

is an active high

test pin and must be maintained low at all times

during normal device operation. In a low-noise

environment, TRST

may be left floating. In other

instances, an external pulldown resistor is highly

recommended. The value of this resistor should be

based on drive strength of the debugger pods

applicable to the design. A 2.2-kΩ resistor generally

offers adequate protection. Since this is

application−specific, it is recommended that each

target board be validated for proper operation of the

debugger and the application. (I ↓)

†

Bold, italicized pin names indicate pin function after reset.

‡

GPIO − General-purpose input/output pin. All GPIOs come up as input after reset.

§

It is highly recommended that V

CCA

be isolated from the digital supply voltage (and V

SSA

from digital ground) to maintain the specified accuracy

and improve the noise immunity of the ADC.

¶

Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

#

No power supply pin (V

DD

, V

DDO

, V

CCA

, V

SS

, or V

SSO

) should be left unconnected. All power supply pins must be connected appropriately for

proper device operation.

LEGEND: ↑ − Internal pullup ↓ − Internal pulldown (Typical active pullup/pulldown value is ±16 µA.)

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145L − JULY 2000 − REVISED SEPTEMBER 2007

17

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

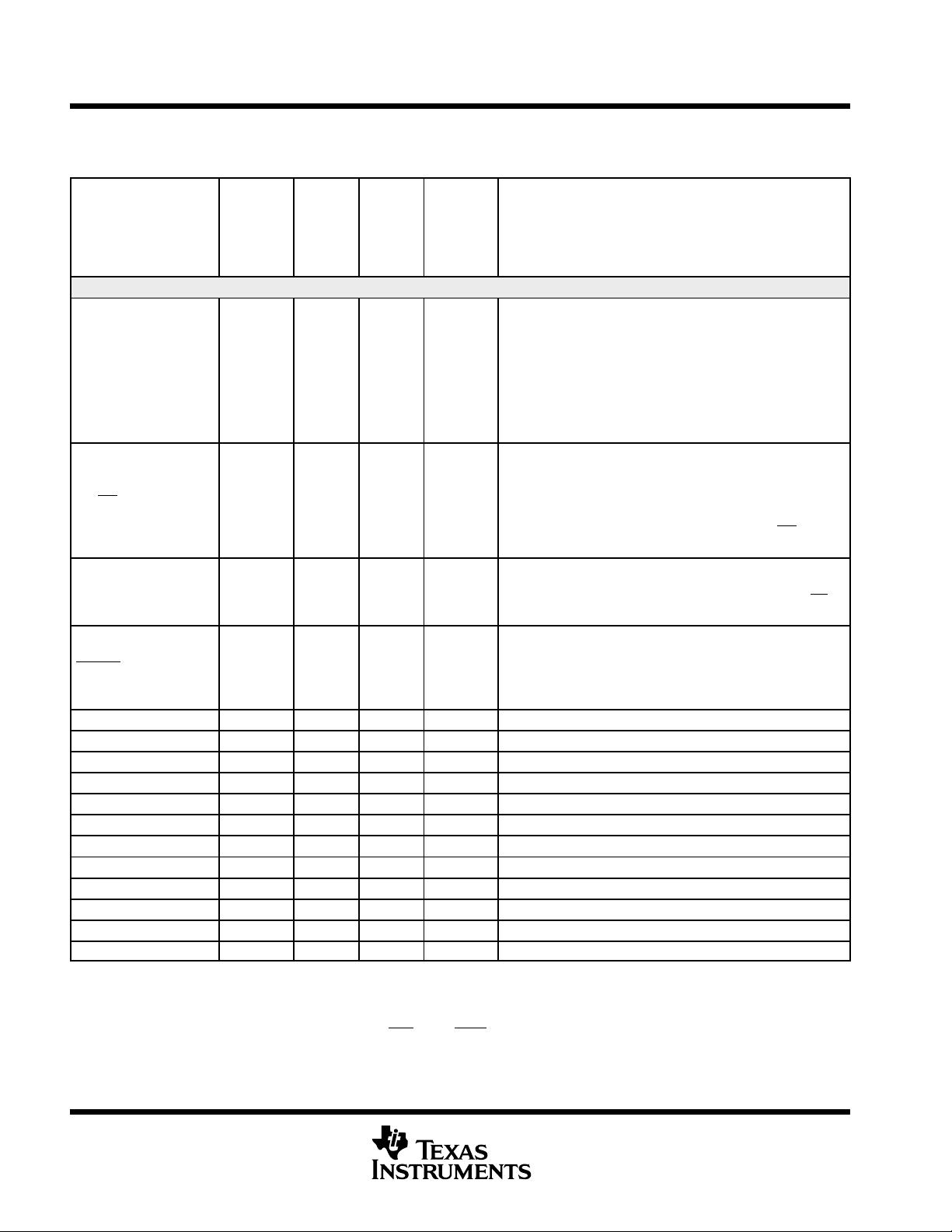

pin functions (continued)

Table 2. LF240xA and LC240xA Pin List and Package Options

†‡

(Continued)

PIN NAME

LF2407A

(144-PGE)

2406A

(100-PZ)

LC2404A

(100-PZ)

2403A,

LC2402A

(64-PAG)

and

2402A

(64-PG)

DESCRIPTION

ADDRESS, DATA, AND MEMORY CONTROL SIGNALS

DS 87

Data space strobe. IS, DS, and PS are always

high unless low-level asserted for access to the

relevant external memory space or I/O. They are

placed in the high-impedance state.

¶

IS 82

I/O space strobe. IS, DS, and PS are always high

unless low-level asserted for access to the

relevant external memory space or I/O. They are

placed in the high-impedance state.

¶

PS 84

Program space strobe. IS, DS, and PS are always

high unless low-level asserted for access to the

relevant external memory space or I/O. They are

placed in the high-impedance state.

¶

R/W 92

Read/write qualifier signal. R/W indicates transfer

direction during communication to an external

device. It is normally in read mode (high), unless

low level is asserted for performing a write

operation. R/W

is placed in the high-impedance

state.

¶

W/R / IOPC0

W/R 19

Write/Read qualifier or GPIO. This is an inverted

R/W

signal useful for zero-wait-state memory

interface. It is normall

y

low

,

unless a memor

y

write

W/R / IOPC0

IOPC0 19 14 14

interface

.

It is normally low

,

unless a memory write

operation is performed. See Table 12, Port C

section, for reset note regarding LF2406A and

LF2402A. (↑)

RD 93

Read-enable strobe. Read-select indicates an

active, external read cycle. RD

is active on all

external program, data, and I/O reads. RD

is

placed in the high-impedance state.

¶

WE 89

Write-enable strobe. The falling edge of WE

indicates that the device is driving the external

data bus (D15−D0). WE

is active on all external

program, data, and I/O writes. WE

is placed in the

high-impedance state.

¶

STRB 96

External memory access strobe. STRB is always

high unless asserted low to indicate an external

bus cycle. STRB is active for all off-chip

accesses. STRB

is placed in the high-impedance

state.

¶

†

Bold, italicized pin names indicate pin function after reset.

‡

GPIO − General-purpose input/output pin. All GPIOs come up as input after reset.

§

It is highly recommended that V

CCA

be isolated from the digital supply voltage (and V

SSA

from digital ground) to maintain the specified accuracy

and improve the noise immunity of the ADC.

¶

Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

#

No power supply pin (V

DD

, V

DDO

, V

CCA

, V

SS

, or V

SSO

) should be left unconnected. All power supply pins must be connected appropriately for

proper device operation.

LEGEND: ↑ − Internal pullup ↓ − Internal pulldown (Typical active pullup/pulldown value is ±16 µA.)

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145L − JULY 2000 − REVISED SEPTEMBER 2007

18

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

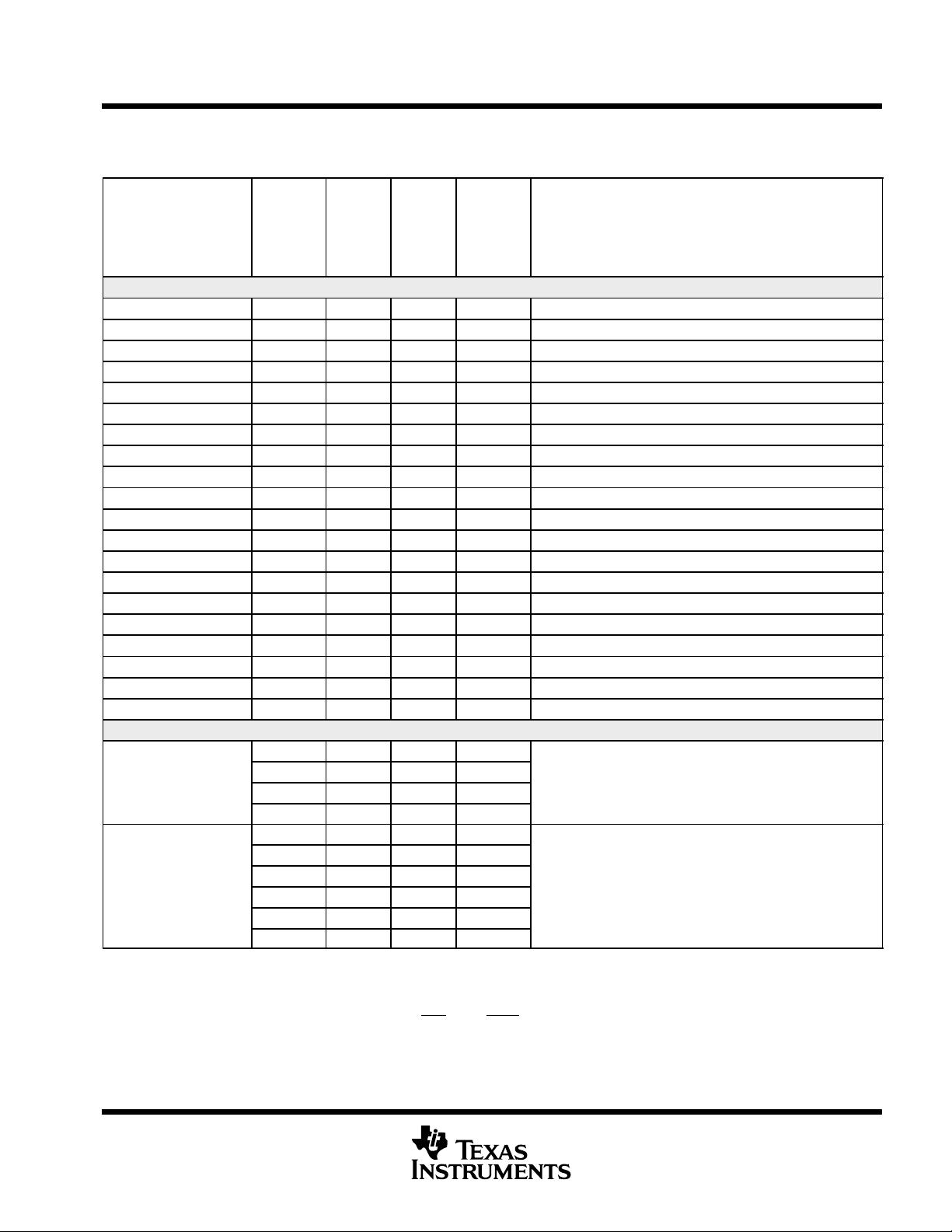

pin functions (continued)

Table 2. LF240xA and LC240xA Pin List and Package Options

†‡

(Continued)

PIN NAME

LF2407A

(144-PGE)

2406A

(100-PZ)

LC2404A

(100-PZ)

2403A,

LC2402A

(64-PAG)

and

2402A

(64-PG)

DESCRIPTION

ADDRESS, DATA, AND MEMORY CONTROL SIGNALS (CONTINUED)

READY 120

READY is pulled low to add wait states for external accesses.

READY indicates that an external device is prepared for a bus

transaction to be completed. If the device is not ready, it pulls the

READY pin low. The processor waits one cycle and checks

READY again. Note that the processor performs

READY-detection if at least one software wait state is

programmed. To meet the external READY timing parameters,

the wait-state generator control register (WSGR) should be

programmed for at least one wait state. (↑)

MP/MC 118

Microprocessor/Microcomputer mode select. If this pin is low

during reset, the device is put in microcomputer mode and

program execution begins at 0000h of internal program memory

(Flash EEPROM). A high value during reset puts the device in

microprocessor mode and program execution begins at 0000h

of external program memory. This line sets the MP/MC

bit (bit 2

in the SCSR2 register). (↓)

ENA_144 122

Active high to enable external interface signals. If pulled low, the

2407A behaves like the 2406A/2403A/2402A—i.e., it has no

external memory and generates an illegal address if DS

is

asserted. This pin has an internal pulldown. (↓)

VIS_OE 97

Visibility output enable (active when data bus is output). This pin

is active (low) whenever the external data bus is driving as an

output during visibility mode. Can be used by external decode

logic to prevent data bus contention while running in visibility

mode.

A0 80 Bit 0 of the 16-bit address bus

A1 78 Bit 1 of the 16-bit address bus

A2 74 Bit 2 of the 16-bit address bus

A3 71 Bit 3 of the 16-bit address bus

A4 68 Bit 4 of the 16-bit address bus

A5 64 Bit 5 of the 16-bit address bus

A6 61 Bit 6 of the 16-bit address bus

A7 57 Bit 7 of the 16-bit address bus

A8 53 Bit 8 of the 16-bit address bus

A9 51 Bit 9 of the 16-bit address bus

A10 48 Bit 10 of the 16-bit address bus

A11 45 Bit 11 of the 16-bit address bus

†

Bold, italicized pin names indicate pin function after reset.

‡

GPIO − General-purpose input/output pin. All GPIOs come up as input after reset.

§

It is highly recommended that V

CCA

be isolated from the digital supply voltage (and V

SSA

from digital ground) to maintain the specified accuracy

and improve the noise immunity of the ADC.

¶

Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

#

No power supply pin (V

DD

, V

DDO

, V

CCA

, V

SS

, or V

SSO

) should be left unconnected. All power supply pins must be connected appropriately for

proper device operation.

LEGEND: ↑ − Internal pullup ↓ − Internal pulldown (Typical active pullup/pulldown value is ±16 µA.)

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145L − JULY 2000 − REVISED SEPTEMBER 2007

19

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

pin functions (continued)

Table 2. LF240xA and LC240xA Pin List and Package Options

†‡

(Continued)

PIN NAME

LF2407A

(144-PGE)

2406A

(100-PZ)

LC2404A

(100-PZ)

2403A,

LC2402A

(64-PAG)

and

2402A

(64-PG)

DESCRIPTION

ADDRESS, DATA, AND MEMORY CONTROL SIGNALS (CONTINUED)

A12 43 Bit 12 of the 16-bit address bus

A13 39 Bit 13 of the 16-bit address bus

A14 34 Bit 14 of the 16-bit address bus

A15 31 Bit 15 of the 16-bit address bus

D0 127 Bit 0 of 16-bit data bus (↑)

D1 130 Bit 1 of 16-bit data bus (↑)

D2 132 Bit 2 of 16-bit data bus (↑)

D3 134 Bit 3 of 16-bit data bus (↑)

D4 136 Bit 4 of 16-bit data bus (↑)

D5 138 Bit 5 of 16-bit data bus (↑)

D6 143 Bit 6 of 16-bit data bus (↑)

D7 5 Bit 7 of 16-bit data bus (↑)

D8 9 Bit 8 of 16-bit data bus (↑)

D9 13 Bit 9 of 16-bit data bus (↑)

D10 15 Bit 10 of 16-bit data bus (↑)

D11 17 Bit 11 of 16-bit data bus (↑)

D12 20 Bit 12 of 16-bit data bus (↑)

D13 22 Bit 13 of 16-bit data bus (↑)

D14 24 Bit 14 of 16-bit data bus (↑)

D15 27 Bit 15 of 16-bit data bus (↑)

POWER SUPPLY

29 20 20 6

V

#

50 35 35 27

Core supply 3 3 V Digital logic supply voltage

V

DD

#

86 59 59 56

Core supply +3.3 V. Digital logic supply voltage.

129 91 91

4 4 4 10

42 30 30 35

V

#

67 47 47 52

I/O buffer suppl

y

+3.3 V. Di

g

ital lo

g

ic and buffer suppl

y

V

DDO

#

77 54 54

I/O buffer supply +3

.

3 V

.

Digital logic and buffer supply

voltage.

95 64 64

141 98 98

†

Bold, italicized pin names indicate pin function after reset.

‡

GPIO − General-purpose input/output pin. All GPIOs come up as input after reset.

§

It is highly recommended that V

CCA

be isolated from the digital supply voltage (and V

SSA

from digital ground) to maintain the specified accuracy

and improve the noise immunity of the ADC.

¶

Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

#

No power supply pin (V

DD

, V

DDO

, V

CCA

, V

SS

, or V

SSO

) should be left unconnected. All power supply pins must be connected appropriately for

proper device operation.

LEGEND: ↑ − Internal pullup ↓ − Internal pulldown (Typical active pullup/pulldown value is ±16 µA.)

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145L − JULY 2000 − REVISED SEPTEMBER 2007

20

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

pin functions (continued)

Table 2. LF240xA and LC240xA Pin List and Package Options

†‡

(Continued)

PIN NAME

LF2407A

(144-PGE)

2406A

(100-PZ)

LC2404A

(100-PZ)

2403A,

LC2402A

(64-PAG)

and

2402A

(64-PG)

DESCRIPTION

POWER SUPPLY (CONTINUED)

28 19 19 5

V

#

49 34 34 26

Core ground Digital logic ground reference

V

SS

#

85 58 58 55

Core ground. Digital logic ground reference.

128 90 90

3 3 3 9

41 29 29 34

66 46 46 51

V

SSO

#

76 53 53

I/O buffer ground. Digital logic and buffer ground reference.

V

SSO

94 63 63

I/O buffer ground. Digital logic and buffer ground reference.

125 97 97

140

†

Bold, italicized pin names indicate pin function after reset.

‡

GPIO − General-purpose input/output pin. All GPIOs come up as input after reset.

§

It is highly recommended that V

CCA

be isolated from the digital supply voltage (and V

SSA

from digital ground) to maintain the specified accuracy

and improve the noise immunity of the ADC.

¶

Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

#

No power supply pin (V

DD

, V

DDO

, V

CCA

, V

SS

, or V

SSO

) should be left unconnected. All power supply pins must be connected appropriately for

proper device operation.

LEGEND: ↑ − Internal pullup ↓ − Internal pulldown (Typical active pullup/pulldown value is ±16 µA.)

剩余134页未读,继续阅读

yyeasayer

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功