FPGA在解决嵌入式系统总线速度瓶颈中的应用

需积分: 31 136 浏览量

更新于2024-09-25

收藏 89KB DOC 举报

"利用FPGA平台解决接口的总线速度瓶颈"

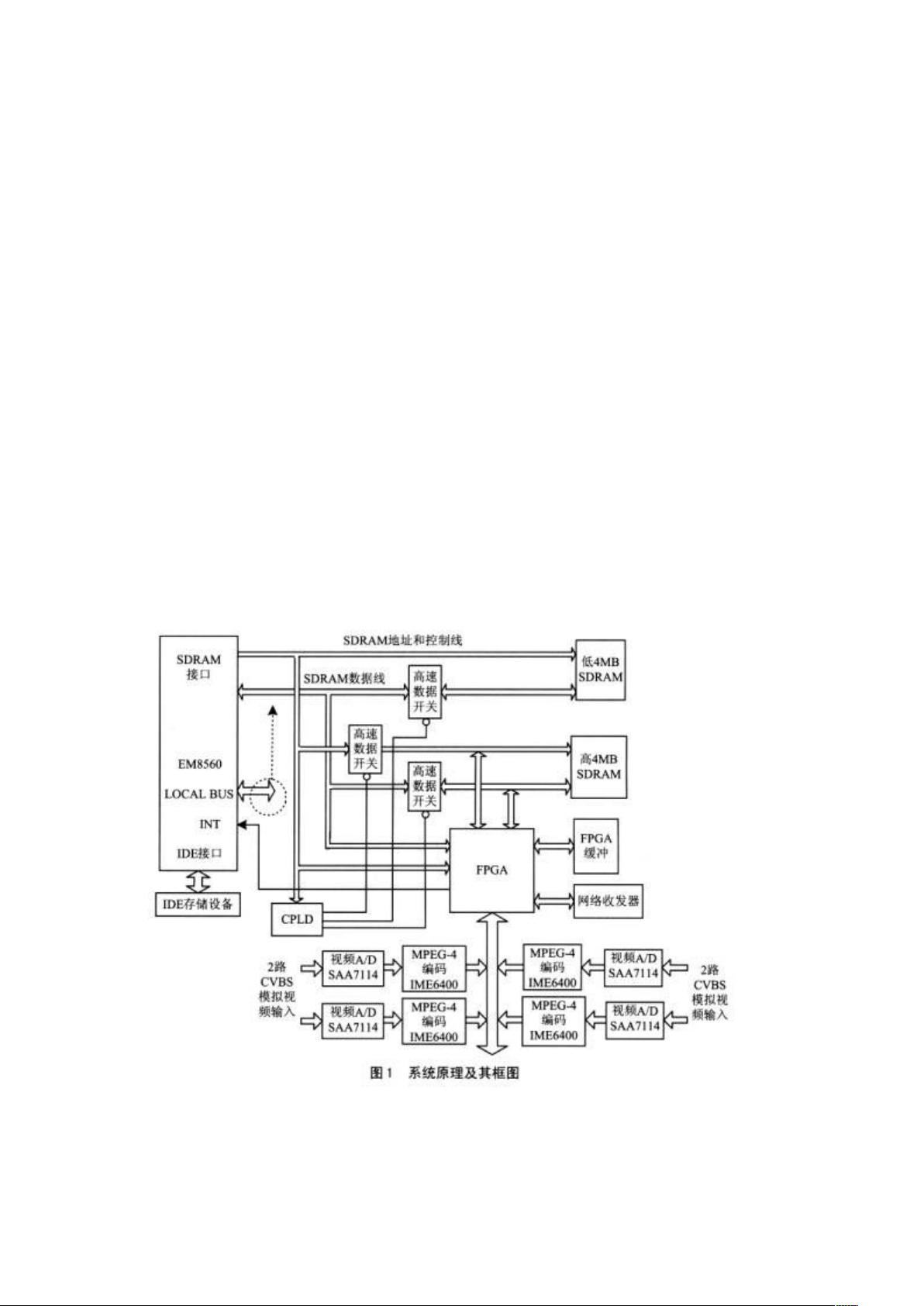

在嵌入式系统设计中,处理器的接口总线速度往往成为系统性能的关键限制因素。本文通过介绍一个基于FPGA(Field-Programmable Gate Array)的解决方案,探讨如何克服这一瓶颈,特别是在实时视频数据存储系统的场景下。嵌入式处理器,如文中提到的SigmaDesign的EM8560,其内部虽集成强大的处理能力,但外部接口的数据传输速率较低,可能导致数据传输延迟,影响整体系统性能。

为了解决这个问题,设计者引入了FPGA作为数据协处理器,并利用CPLD(Complex Programmable Logic Device)进行主处理器与协处理器之间的数据通信管理。FPGA因其高度可配置性和并行处理能力,能有效提升数据处理速度,而CPLD则用于优化控制逻辑,确保高速数据传输的同步性。

系统架构包括四个主要部分:嵌入式处理器(EM8560)、CPLD、FPGA以及视频图像压缩输入部分。EM8560的IDE接口和LocalBus总线虽支持多种标准,但其异步传输方式导致数据传输速率较低。为满足高带宽需求,FPGA被用来加速数据处理,而CPLD则确保FPGA与嵌入式处理器间的数据交换快速且无误。

视频图像压缩输入部分采用Philips的SAA7114进行模拟信号到数字信号的转换,再由IME6400编码芯片进行MPEG-4编码。IME6400的1KB输出缓冲区要求在400us内读取完毕,否则新数据会覆盖旧数据,导致视频数据丢失。这是总线速度瓶颈带来的直接影响。

为解决这个问题,FPGA被配置为数据缓冲和高速数据处理单元,它可以并行处理多个数据流,显著提高数据吞吐量。同时,CPLD负责协调主处理器和FPGA之间的数据传输,确保在IME6400的缓冲区清空之前,数据已被及时读取和处理。

该设计方案展示了如何利用FPGA的并行处理能力和CPLD的灵活控制逻辑,改善嵌入式系统中的总线速度瓶颈问题,从而提高系统的实时性能,特别是对于那些对数据传输速度有严苛要求的应用,如实时视频处理。这样的方法对其他类似面临接口速度限制的嵌入式系统设计具有广泛的借鉴意义。

109 浏览量

274 浏览量

122 浏览量

2021-07-13 上传

2012-05-16 上传

257 浏览量

169 浏览量

点击了解资源详情

点击了解资源详情

Augusdi

- 粉丝: 1w+

- 资源: 5737

最新资源

- python编码规范

- 企业真实的项目文档(需求分析及详细设计)

- 2008年4月计算机等级二级C语言练习题及答案

- AbrastractExecutorService

- PCB 工艺设计规范

- SQL数据要求说明书

- KillTest 310-065 Demo

- 网上图书网站设计和论文

- 2009思科路由协议挑战100问.pdf

- 数据结构算法与应用-C__语言描述2

- 数据结构算法与应用-C__语言描述

- 无线传感器网络路由协议研究综述(硕士研究生论文)

- WISECMS模板标签说明

- Learning+jquery中文版 第一章

- JSP+structs网上书店cookie实现

- Hardware-Dependent Software Principles and Practice