P1: IML/FFX P2: IML

MOBK046-01 MOBK046-Thornton.cls October 14, 2006 13:14

DIGITAL LOGIC REVIEW WITH VERILOG QUICKSTART 9

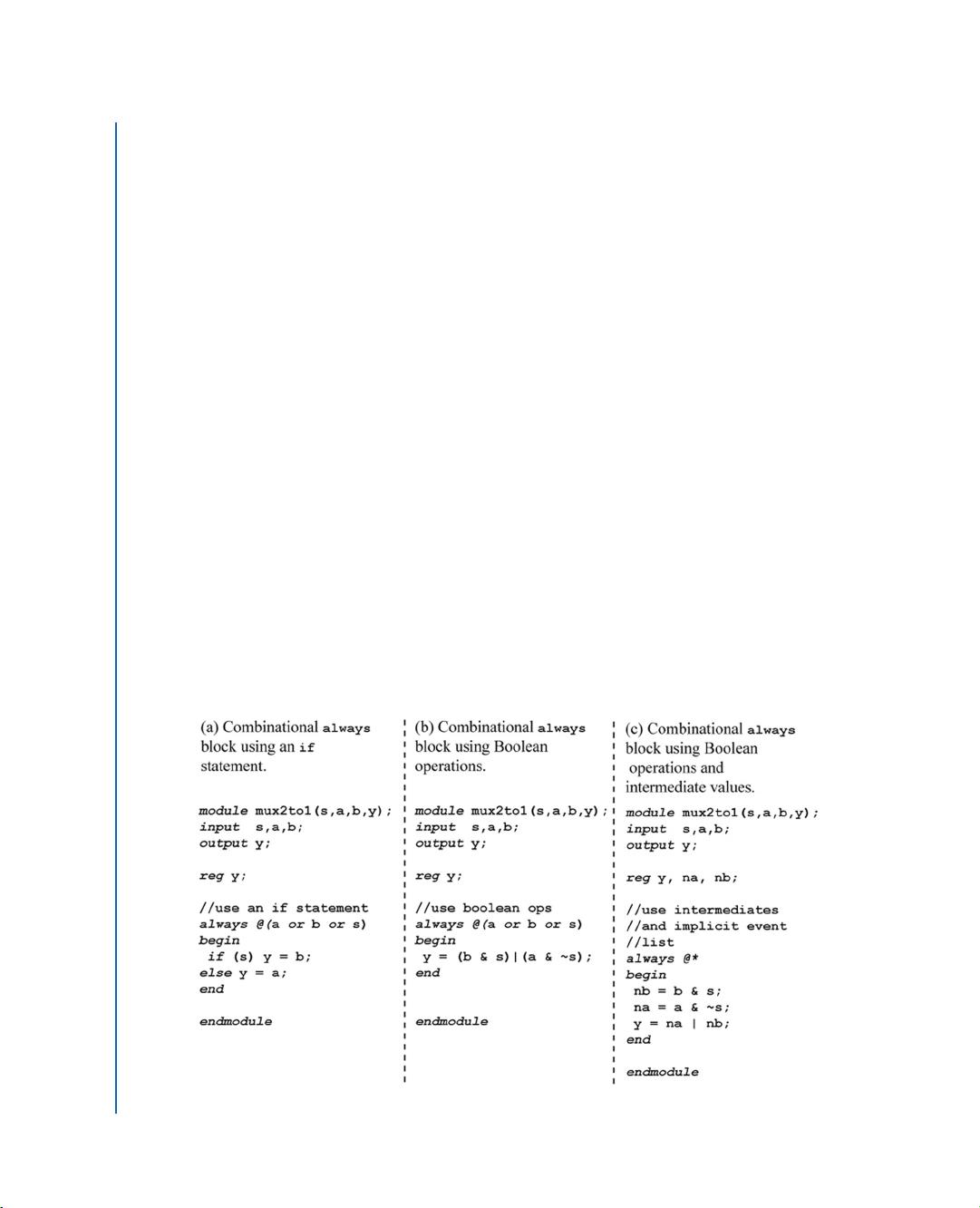

of an always block can be one or more statements; begin and end keywords are used to

group multiple statements. The statement “

reg y;

” is included in each of the three modules

of Fig. 1.8 as any net that is assigned within an

always block must be declared as a reg type;

this does not imply that this net is driven by a register or sequential logic.

Fig. 1.8(a) implements the multiplexer using an

if-else statement, with the if-body

evaluated for a nonzero (true) conditional expression and the

else clause evaluated otherwise.

Keywords

begin

and end can be used to place multiple statements in an if-body or else clause.

Fig. 1.8(b) implements the multiplexer using Boolean operators, while Fig. 1.8(c) distributes

the Boolean operators using intermediate nets and multiple assignments. The “=” operator

when used in an

always block is called a blocking assignment, this terminology is discussed in

more detail in Section 1.6, which covers event-driven simulation principles. The

always block

of Fig. 1.8(c) uses an implicit event list designated by “

@

∗

,” which means that all nets on the

right side of the assignments are included in the event list.

The semantics of the net assignments in an

always blocks differs significantly from

assign

statements in that statements in an

always

block use the same sequential execution

model as the statements in an HLL.

•

The logic synthesized for an

always block duplicates the assignments’ behavior as-

suming that the assignments are evaluated sequentially. This means that the order in

which assignments are written in an

always blocks affects the logic that is synthesized.

•

Because of the sequential nature of an

always block, the same net can be assigned

multiple times in an

always block; the last assignment takes precedence.

Fig. 1.9 shows a case in which multiple blocking assignments are made to a net in the same

always block, with assignment ordering affecting the synthesized logic. In Fig. 1.9(a), the

clr input takes precedence over the ld input if both are “1,” while in Fig. 1.9(b) the opposite

holds true. Observe that in the two

always blocks, if both ld and clr are “0,” then the initial

assignment of

q=q old sets the value of q. This is a common coding style used in combinational

logic

always blocks in that a default assignment is made to an output at the block’s beginning,

which is then overridden by later assignments in the block based upon the assertion of other

inputs.

The use of a default assignment to the output net of a combinational

always block

guarantees that the output net is the target of an assignment for any input combination. If there

is some logic path through the

always block that does not assign a value to the output net, then

a latch is inferred on that output as shown in Fig. 1.10. A latch is a sequential logic element,

and should not be synthesized in an

always block that is meant to implement combinational

logic. Inferred latches are a common coding mistake for users who are new to Verilog and logic