ModelSim Verilog仿真入门教程

需积分: 10 46 浏览量

更新于2024-09-15

收藏 684KB PDF 举报

"ModelSim6.1入门教程,包括如何建立工程、编写Verilog代码和进行编译"

在本文中,我们将深入探讨ModelSim的基础使用,这是一个广泛用于验证数字逻辑设计的仿真工具。ModelSim适用于Verilog HDL(硬件描述语言)的学习和开发,通过它,用户可以测试和调试他们的电路设计。

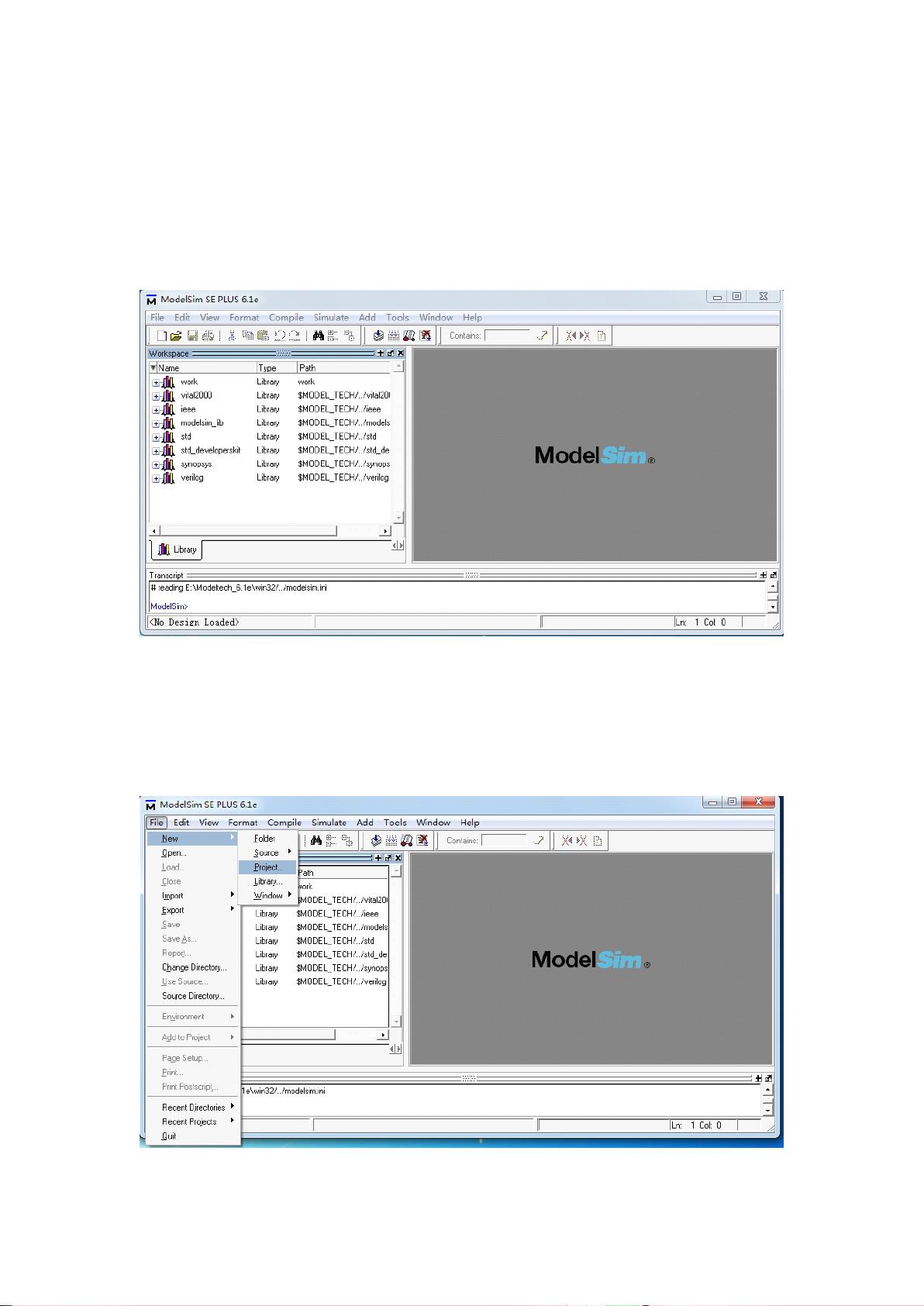

1. **启动与界面介绍**

ModelSim的界面布局清晰,易于理解。主界面由四个主要部分组成:

- 菜单栏:提供各种功能的访问入口。

- 工作空间栏:显示当前项目的文件结构,包括库文件。

- 编辑栏:用于编写和查看Verilog源代码。

- 交互区:允许用户输入命令进行仿真和其他操作。

2. **创建工程**

创建新工程是使用ModelSim的第一步。在"Project"菜单下选择新建项目,命名为"AND_2",并指定存放路径。默认库通常设置为"work"。点击"OK"后,工程会出现在工作空间中,状态为"?",表示尚未编译。

3. **编写Verilog代码**

双击工作空间中的"AND_2"文件打开编辑器,输入一个简单的AND门电路的Verilog代码。这个模块接收两个输入(A和B),一个时钟(clk)和一个复位信号(rst),并有一个输出(C)。`always @(posedge clk or negedge rst)`块定义了敏感列表,当时钟上升沿或复位信号下降沿时,该块内的代码会被执行。

4. **保存与编译**

保存代码后,要确保模块名(AND_2)与工程名一致,这是编译通过的关键。右键点击工作空间中的"AND_2",选择"Compile" -> "Compile All"。在交互区的Transcript中,如果出现绿色的"Compile of AND_2 was successful.",说明编译成功。

5. **仿真**

编译成功后,下一步是进行仿真。这通常涉及设置波形观察点、配置激励和运行仿真。在ModelSim中,你可以通过命令行或图形用户界面设置这些参数。例如,你可能需要为输入端口分配值,然后启动仿真(`run`命令)。在仿真过程中,你可以观察输出端口的变化,检查电路行为是否符合预期。

6. **查看波形**

ModelSim的波形视图是调试设计的重要工具。在编译完成后,可以通过"View"菜单选择"Waveform Viewer"来打开波形窗口。在这里,你可以添加信号到波形窗口,查看它们随时间的变化,以直观地理解设计的运行情况。

ModelSim提供了一个强大的环境来验证Verilog设计。从创建工程、编写代码、编译到仿真和分析结果,每个步骤都有清晰的指导。随着对ModelSim的熟悉和熟练使用,开发者能够更有效地调试和优化他们的数字电路设计。

点击了解资源详情

点击了解资源详情

点击了解资源详情

179 浏览量

2009-04-09 上传

114 浏览量

2010-12-28 上传

319 浏览量

2008-12-18 上传