DLPC350控制器与DMD的高速PCB布线规范

需积分: 9 84 浏览量

更新于2024-09-06

收藏 243KB DOCX 举报

"DLP350芯片的PCB布线规则,强调高速信号处理,如HDMI和DMD信号部分,需要考虑阻抗匹配、长度控制和等长要求。文档提供了PCB设计指南,包括组件操作的正确保证,推荐采用特定的配置、蚀刻厚度、信号阻抗、道宽、最小间距以及线路限制。对于DMD接口的信号,有特定的长度线路约束和高速信号匹配要求。"

DLP350芯片在PCB设计中扮演着关键角色,因为它是高速逻辑电路的一部分,涉及到高速数字接口,例如120MHz DDR接口到DMD、150MHz LVTTL接口从视频解码器到DLPC350、150MHz像素时钟以及LVDS平板显示端口。这些接口的正确运行需要精细的PCB布线策略。

根据文档,PCB设计应遵循IPC2221和IPC2222标准的2级,Z型,B级可生产性,同时制造过程需符合IPC6011和IPC6012规定。在设计过程中,应特别注意以下几点:

1. **配置与阻抗匹配**:推荐采用不对称双带状线配置,单端信号阻抗应设定为50Ω,差分信号阻抗为100Ω差动,允许10%的误差范围。

2. **道宽与最小间距**:TI提供了具体的道宽和最小间距建议,这对于确保信号的完整性和减少干扰至关重要。这些参数会直接影响信号的质量和稳定性。

3. **线路限制**:为满足信号线路长度规范,部分信号可能需要手动布线,尤其是对于长度匹配要求严格的信号,可能需要使用蛇形布线来调整长度。最小转弯角度建议为45°,且迹线距离板边缘至少0.1英寸,以减少信号损失和串扰。

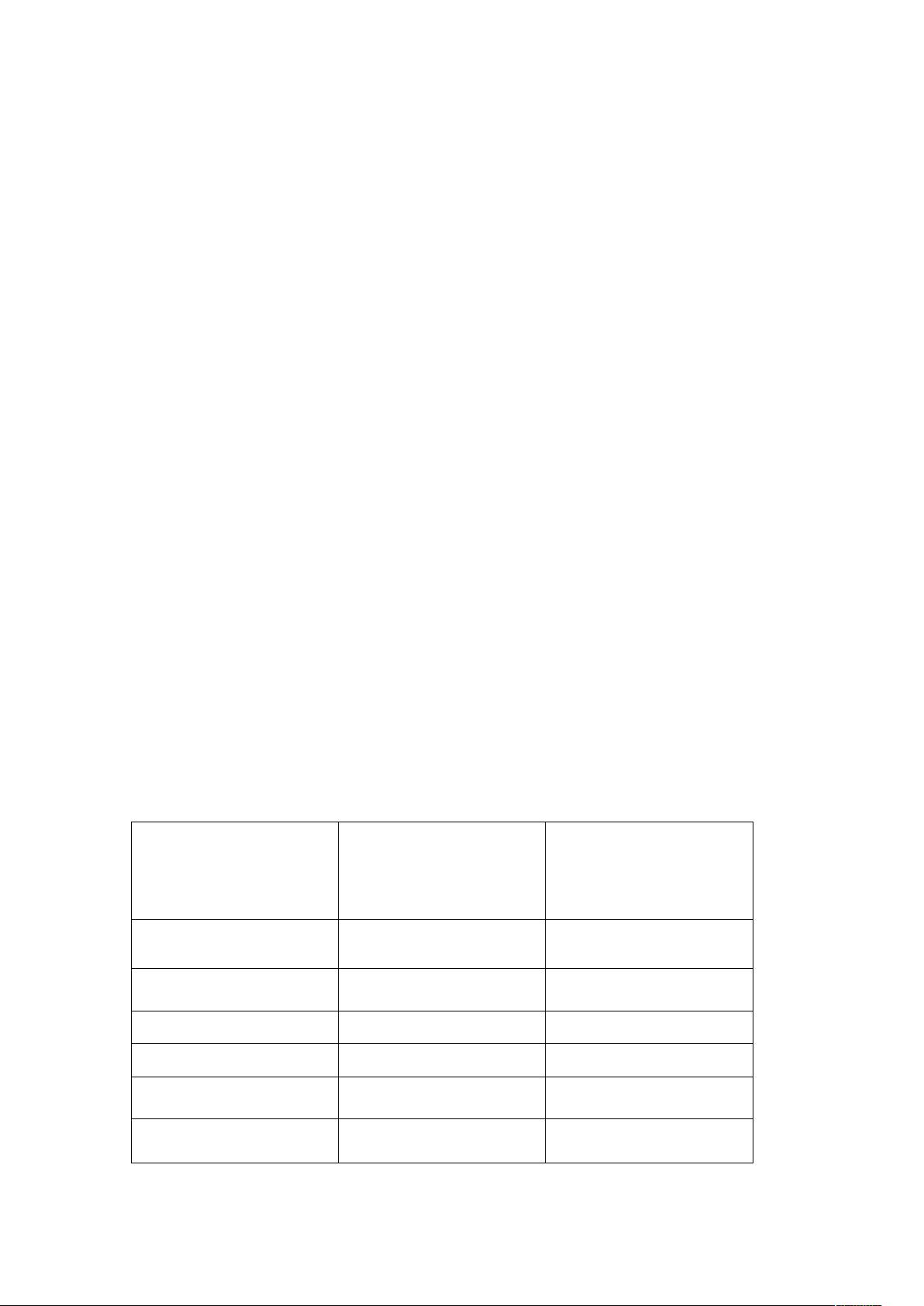

4. **DMD接口的信号长度线路约束**:表20列出了DMD接口信号的最小和最大线路长度限制,长度不达标可能导致过冲或下冲。DMD-DDR的最大信号长度取决于DMD_DCLK速率。

5. **高速信号匹配要求**:表21给出了DMD接口高速信号的匹配要求,确保每个高速单端信号与参考信号保持恒定阻抗,同时避免急剧转弯和层间切换,以减少信号失真并保持总迹线长度最小。

在实际PCB设计中,还需要考虑PCB的热管理、电源平面的分割、噪声隔离、去耦电容的放置等其他因素,以确保整个系统的稳定性和可靠性。这些指导原则和参数是确保DLP350芯片及与其交互的高速信号高效、无误传输的关键。

zxq46964890

- 粉丝: 0

- 资源: 4

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库