JEDEC Standard No. 400-5

Page 8

5 Parsing the SPD (cont’d)

New in DDR5 SPD contents definition is a separate revision byte for sections of the contents. For example, the

revision byte 1 covers only the base configuration information blocks, bytes 0 to 127. There is a separate revision

byte for other sections such as the standard module parameters in bytes 192-447. The same scheme of contents and

additions nibbles is used in each of these sections to allow forward and backward compatibility. Having separate

revision levels in various sections of the SPD contents allows those sections to change independently.

Step 4: Parse Byte 3 - Determine module type and appropriate overlays.

Key byte 3 for module type determines the subsequent use of overlay information. Byte 3 defines the host to module

interface style: unbuffered, registered, load reduced, differential, or hybrid. Standard module types are defined in

Annexes A.x.

Step 5: Parse Bytes 0~127 - Make base configuration settings to memory interface based on these bytes.

All module types are required to read and interpret this block of data to set up the DRAM type, maximum operating

frequency, the number of row, column, bank bits, write recovery time, etc. While these bytes primarily describe the

timing of the DRAMs, timing represents the capabilities of the module and it may be necessary to downgrade the

timing based on other factors including layout or support components on the module, such as registers.

Step 6: Parse Byte 192 - Module-specific annex SPD revision.

This byte determines the encoding level and additions level of the module specific bytes of the SPD. Separating the

base section of the SPD and module specific section prevents unnecessary churn; for example, if the UDIMM annex

changes, the SPD for RDIMM/LRDIMM module need not change.

Step 7: Parse Bytes 193~447 - Configure standard module memory interface.

These bytes will be referenced and used by the system as needed based on the Standard module type that was

determined after Byte 3 was parsed as indicated in Step 2. Bytes 192~239 are common byte definitions for all module

types as defined in Annex A.0. Bytes 240~447 are coded differently for each standard module type as defined in

Annex A.x.

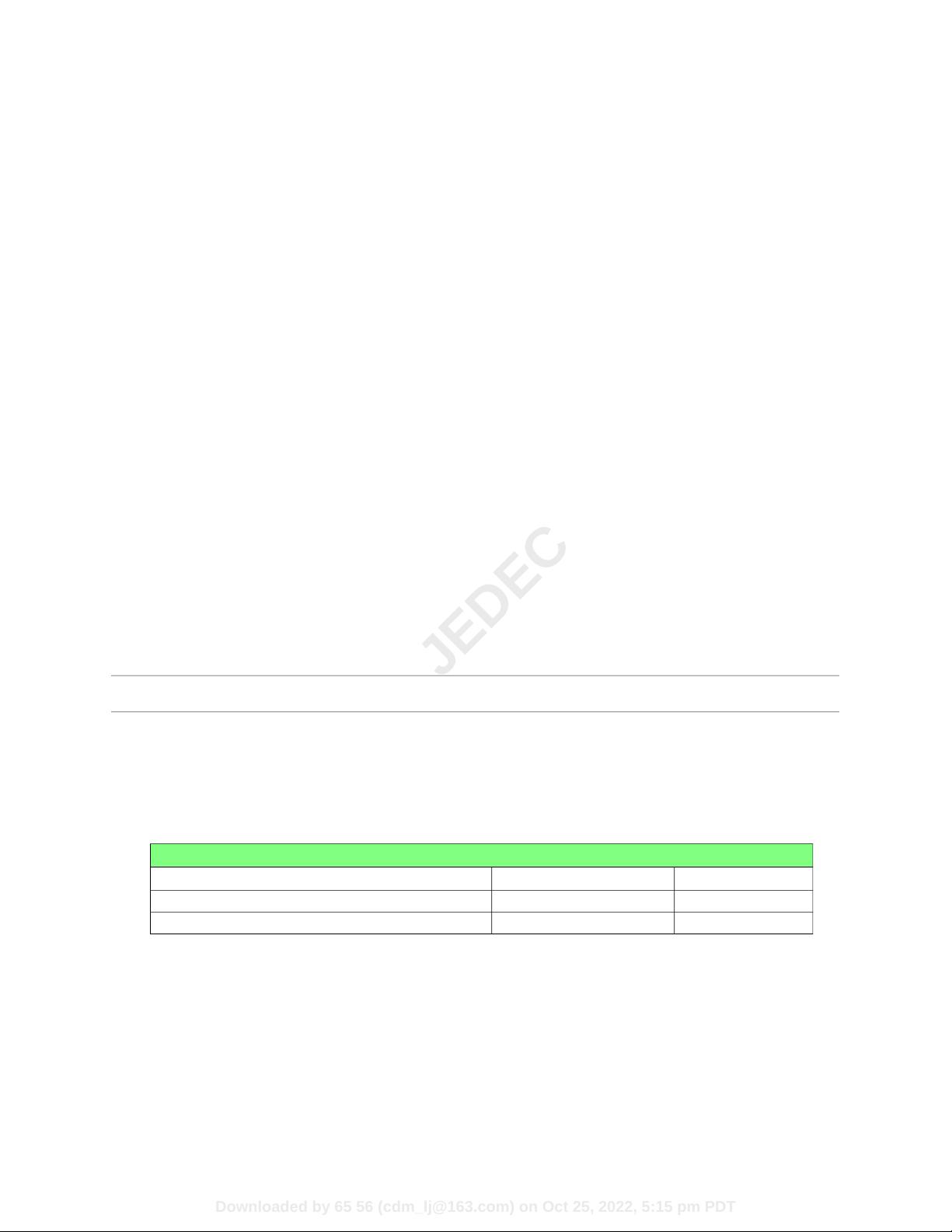

6 SPD Revision Progression

SPD Contents sections have a revision code for that section of the specification. This allows each section to evolve

over time independently as much as possible. For example a system may need to parse one revision level for the Base

Configuration section (bytes 0~127) and a different revision level for the Standard Module Parameters section (bytes

192-447).

The Additions Level is never reduced even after an increment of the Encoding Level. For example, if the current SPD

revision level were 1.2 and a change in Encoding Level were approved, the next revision level would be 2.2. If

additions to revision 2.2 were approved, the next revision would be 2.3. Changes in the Encoding Level are extremely

rare, however, since they can create incompatibilities with older systems.

The exceptions to the above rule are the SPD revision levels used during development prior to the

Revision 1.0 release. Revisions 0.0 through 0.9 are used to indicate sequential pre-production SPD revision levels,

however the first production release will be Revision 1.0.

Hypothetical SPD Revision Progression Showing Revision Relationships

Section

Bytes

Revision Byte

Base Configuration and SDRAM Parameters 0~127 1

Standard Module Parameters 192~447 192

Downloaded by 65 56 (cdm_lj@163.com) on Oct 25, 2022, 5:15 pm PDT

JEDEC