使用SystemC构建MIPS CPU:从基础知识到指令流程

"本文档是关于如何使用SystemC设计MIPS CPU的一个教程,涵盖了SystemC的基本知识、MIPS指令流程以及使用SystemC实现MIPS CPU的步骤。"

SystemC是一种高级的硬件描述语言,它基于C++,专为系统级建模、仿真和综合而设计。随着电子产品开发周期的缩短和基于平台的设计复杂度增加,SystemC应运而生,它提供了一种快速构建可执行模型的方法,能够在较高抽象层次上表示底层电路。SystemC有可能成为IEEE标准,对于希望从事系统设计的人来说,掌握它是很有帮助的。

在学习SystemC之前,需要具备C++基础和逻辑设计的知识。如果你已经熟悉VHDL或Verilog这两种硬件描述语言,学习SystemC会更加容易。

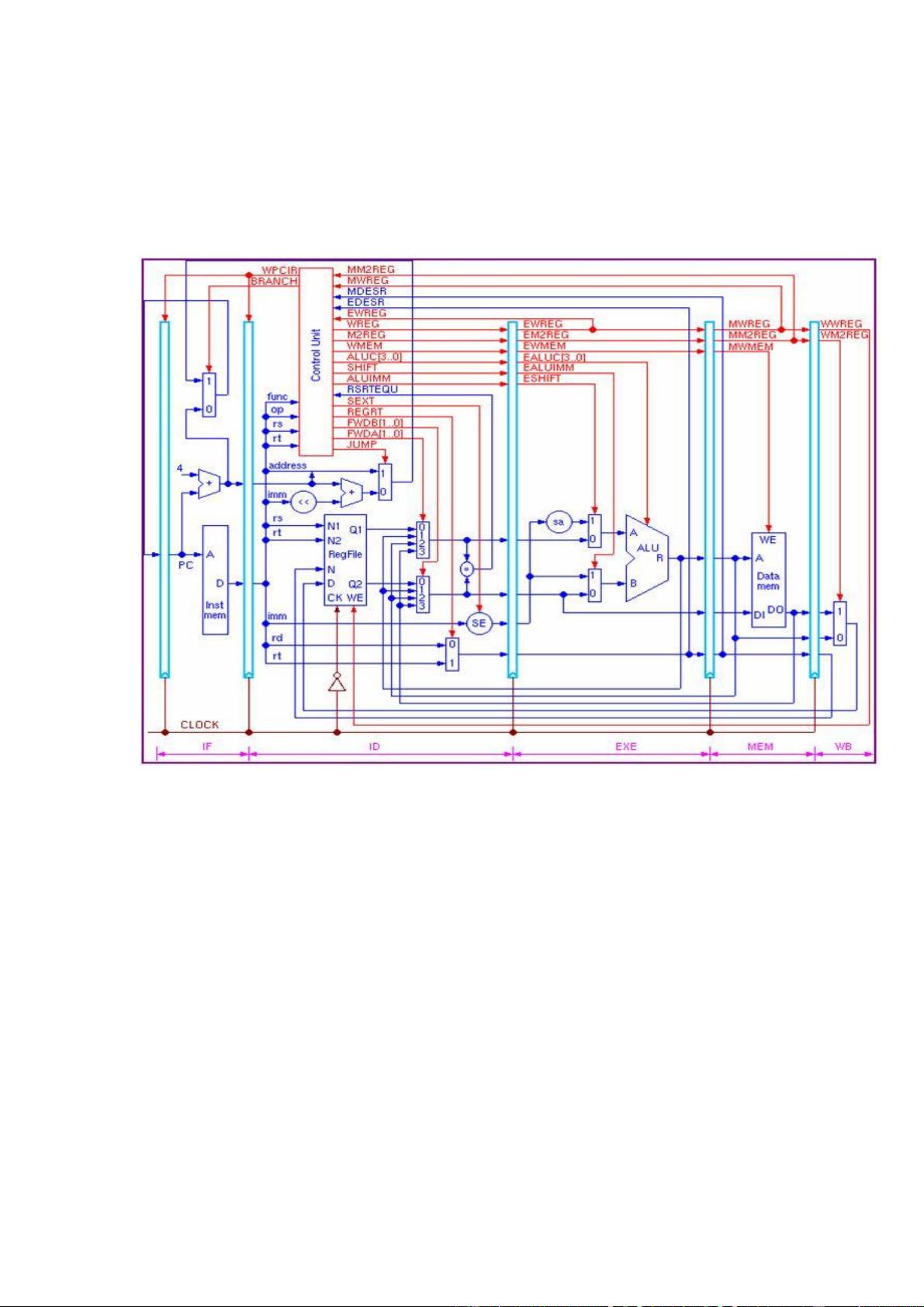

MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集计算机(RISC)架构,以其简单性和高效性而闻名,常用于CPU设计的教育和实践。MIPS的指令执行分为5个阶段:取指(IF)、译码(ID)、执行(EXE)、内存访问(MEM)和写回(WB)。每个阶段都有对应的寄存器来存储信息,并通过锁存器进行传递。例如,在IF阶段,程序计数器(PC)用于获取指令地址,然后更新PC并选择是否根据ID阶段的跳转指令改变地址。

MIPS指令集包括三种基本类型:I型指令(包含立即数)、R型指令(包含目的寄存器)和J型指令(跳转指令)。在ID阶段,需要对这三种类型的指令进行解码,以便执行相应的操作。例如,I型指令通常用于数据传输或算术运算,R型指令用于处理寄存器之间的操作,而J型指令则用于控制流程转移。

使用SystemC设计MIPS CPU时,可以利用其模块化特性,将每个阶段和相关组件(如ALU、寄存器文件、数据通路等)建模为独立的类。这些类可以通过接口进行通信,模拟指令的执行流程。SystemC的事件驱动模型使得能够方便地模拟时序行为,从而在软件层面验证CPU设计的功能正确性。

通过这种方式,设计师可以提前发现设计中的错误,减少硬件原型的迭代次数,提高设计效率。此外,SystemC还可以与硬件描述语言(如VHDL和Verilog)结合,进行高层次综合,直接生成FPGA或ASIC实现的网表。

总结来说,本教程将指导读者如何利用SystemC来设计MIPS CPU,从理解SystemC的基础,到解析MIPS指令,再到实际构建CPU模型,内容详尽且实用。对于希望深入理解硬件设计和系统级建模的工程师来说,是一份宝贵的参考资料。

相关推荐

pigoneand

- 粉丝: 8

最新资源

- 易语言实现数字转汉字大写功能详解

- 深入探索密码学技术及实施方案

- Radmin 3.4中文版及NewTrialStop 2.3破解教程

- Quartus2实现正弦波发生器的设计与应用

- SimpleBinaryEditor:直观展现二进制数据的Python工具

- 普通车床主传动系统设计方案分析

- 易语言实现员工信息管理系统教程

- 掌握VC调试技术的快速入门指南

- 深入浅出Activiti工作流引擎实战应用

- 使用OMDB API打造的电影数据库网站

- 电脑端预览PPC手机桌面主题的DLL插件

- ANSYS流固耦合分析实例探讨

- 掌握有米Android广告SDK的集成与实例

- 易语言实现的易乐谷机器人对话工具功能详解

- Spotipy-Python实践指南:轻松掌握音频分析

- nrComm.XE5 串口通信库:支持多设备接入与短信功能