高性能 Invensense INMP441 数字硅麦:适用于多种高端设备

需积分: 9 96 浏览量

更新于2024-07-19

收藏 466KB PDF 举报

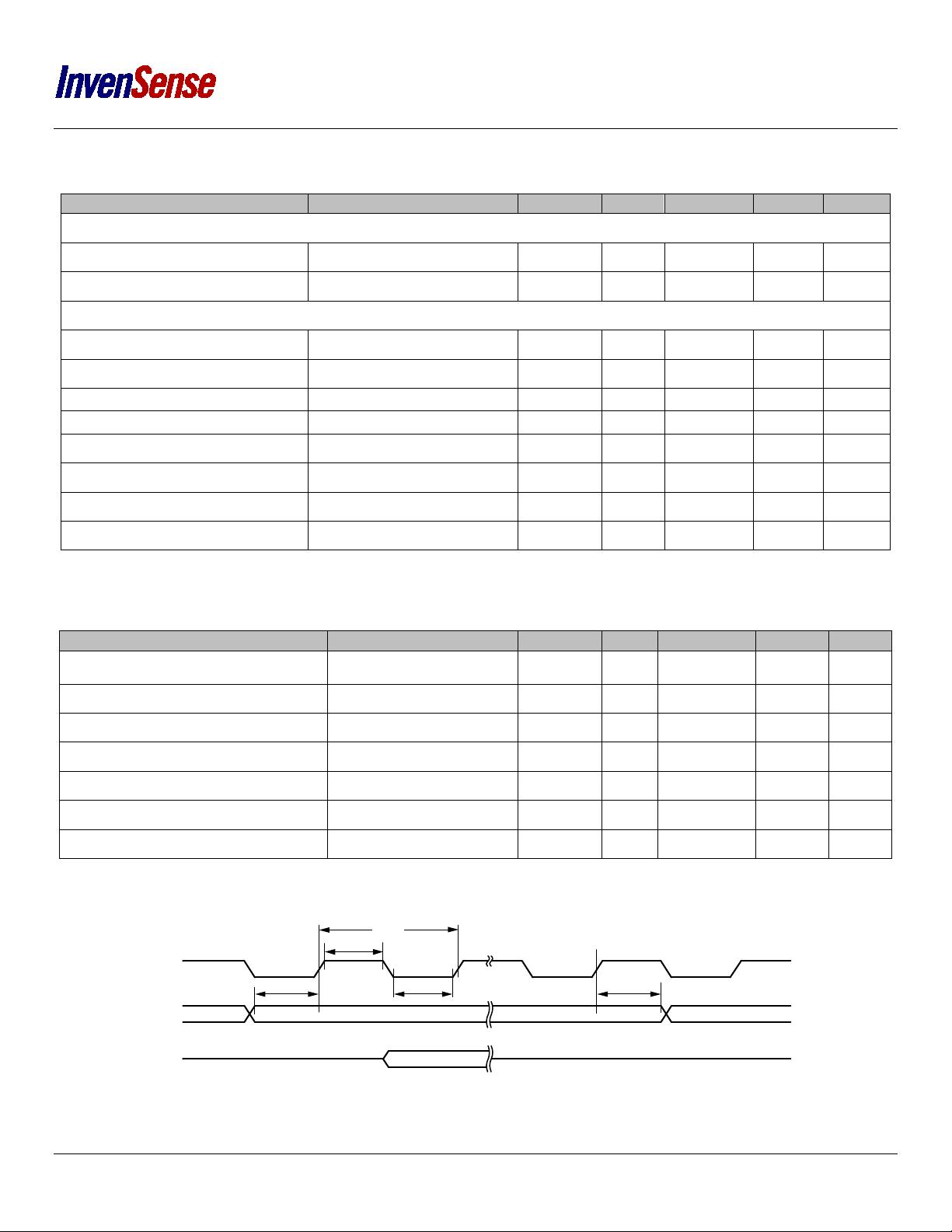

"Invensense INMP441 数字硅麦是一款高性能、低功耗的全方位数字输出微型麦克风,适用于多种应用场景,如远程会议系统、遥控器、游戏机、移动设备和笔记本电脑等。该产品集成有MEMS传感器、信号调理电路、模数转换器、抗混叠滤波器、电源管理和标准的24位I²S接口。"

Invensense INMP441 是Invensense公司推出的一款高级数字麦克风,它在音频捕捉和处理方面表现出色。这款硅麦的核心特性在于其数字输出功能,能够直接与数字处理器(如DSPs和微控制器)连接,无需额外的音频编解码器,简化了系统设计。I²S接口是其一大亮点,它是一种广泛应用于音频设备的标准接口,能确保数据传输的高效和稳定性。

在性能上,INMP441具有高信噪比(SNR),这意味着它在近场应用中能捕获到清晰、无噪声的声音,非常适合需要高质量音频输入的场景。此外,它的宽频带频率响应平坦,使得录制的声音自然且具有高可理解性,增强了语音和音频的清晰度。

在物理设计上,INMP441采用了一个薄型的4.72×3.76×1mm贴片封装,适应现代电子产品的紧凑空间需求。它还支持回流焊工艺,焊接后不会影响性能,并且是无卤素设计,符合环保要求。该产品已获得多项美国专利保护,并且还有其他专利正在申请中,显示出其在技术上的创新性和独特性。

应用领域广泛,包括但不限于:

1. 远程会议系统:在视频会议中提供清晰的语音通信。

2. 遥控器:提高智能遥控器的语音指令识别能力。

3. 游戏机:增强游戏内的语音交流体验。

4. 移动设备:如智能手机和平板电脑,用于语音识别、通话和录音功能。

5. 笔记本电脑:提升内置麦克风的音质,适用于在线会议和语音输入。

Invensense INMP441 数字硅麦是一款集高性能、低功耗、小巧便携于一身的麦克风解决方案,适合对音频质量有较高要求的各类电子产品。其独特的技术特点和广泛应用场景,使其在IT行业中具有很高的价值。

285 浏览量

2014-07-11 上传

2022-09-21 上传

2013-07-24 上传

2023-05-17 上传

2019-03-07 上传

2019-03-07 上传

2013-07-24 上传

点击了解资源详情

Jesseb

- 粉丝: 0

- 资源: 3

最新资源

- Mobile移动开发宝典_第01章 .NET Compact Framework移动平台

- 高质量C++编程指南

- 空间数据库备份恢复arcgisdb

- Linux下omnet++4.0 Tictoc

- 我自己寫的一些簡單代碼

- PC机与多MCS_51单片机间的串行通信设计

- cairngorm 经典的一个例子

- BB典、实用、趣味程序设计编程百例精解BB典、实用、趣味程序设计编程百例精解

- MapServer.Open.Source.GIS.Development.Aug.2005

- matlab simulink资料,特适合初学者

- JavaScript 高级程序设计[精华].pdf

- 单片机毕业设计——可编程微波炉控制器系统设计

- 留言板的jsp代码+数据库设计+页面结构

- GNU-Make中文说明

- Ajax技术地图,是了解ajax的好工具。适合ajax的初学者了解整体脉络哦!

- linux_mig_release_G4oyxcsIVyIZ