FPGA实现UART扩展总线设计及驱动程序

82 浏览量

更新于2024-08-29

1

收藏 199KB PDF 举报

"基于FPGA 的UART 扩展总线设计和应用"

在当前的嵌入式系统中,随着系统功能的日益集成,对外设的控制需求也在不断增加。UART(通用异步收发传输器)因其简易的操作、高可靠性、强抗干扰能力以及远距离传输特性(例如在485网络中可超过1,200米)而在工业、通信及家电控制等领域广泛应用。然而,大多数处理器仅配备了一个内置的UART串口,这在实际项目中往往不足以满足需求。因此,扩展UART总线成为了必要的解决方案。

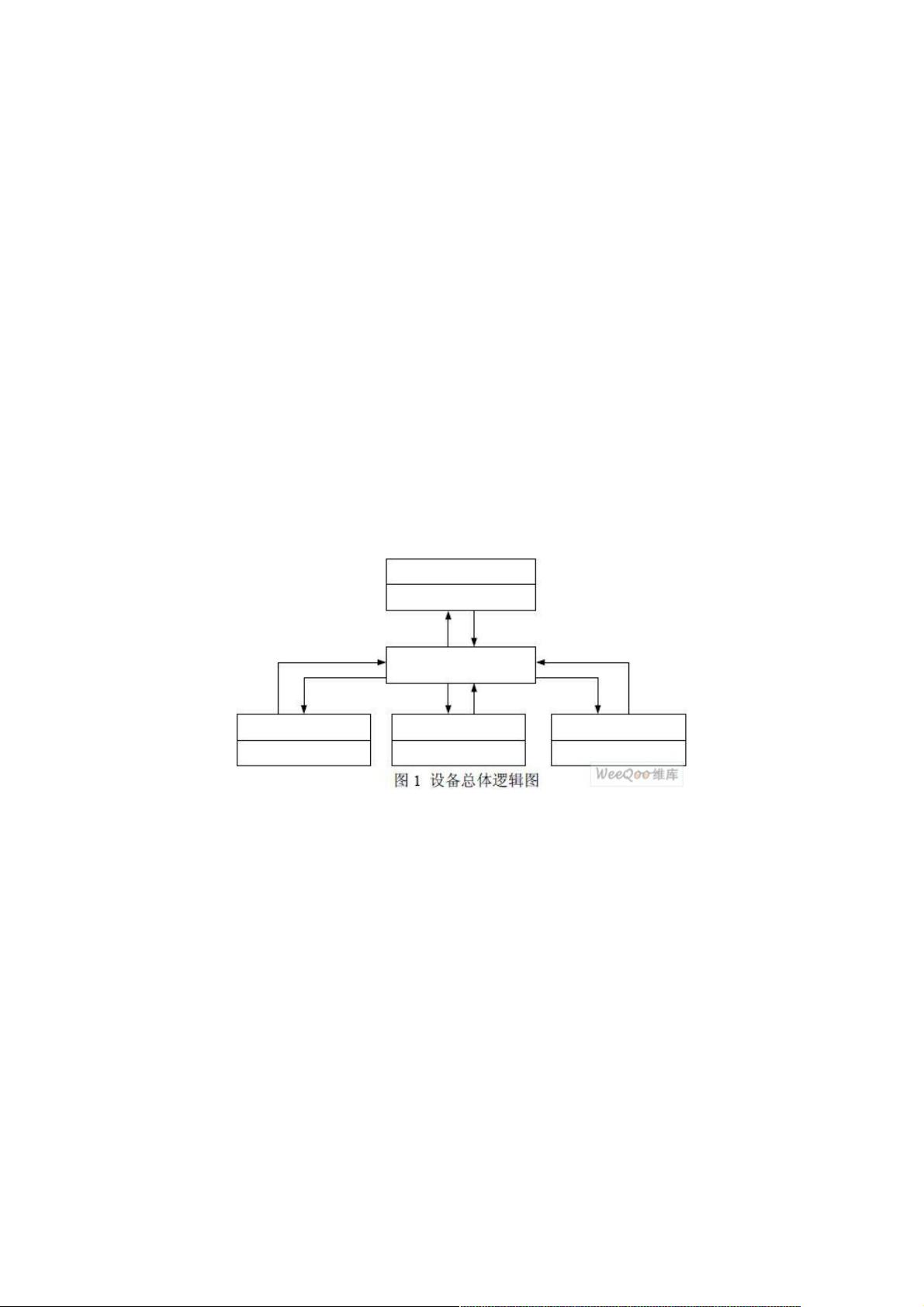

本文聚焦于使用FPGA(现场可编程门阵列)实现UART扩展总线的设计和相关驱动程序开发。首先,介绍了FPGA作为实现UART扩展的核心技术,它能灵活地配置逻辑以适应不同的外设接口需求。在FPGA设计中,通常会结合片上总线技术,如WISHBONE,来实现多个逻辑模块之间的通信。

在WISHBONE总线设计中,它采用主从架构,即一个主单元(MASTER)发起与一个或多个从单元(SLAVE)的数据传输。主从之间的通信通过握手协议确保数据传输的正确性,这种机制保证了在高速和低速设备共存时的兼容性和稳定性。

在具体的实现中,如文中提到的嵌入式系统,使用了AT91ARM9200处理器,它运行Linux操作系统,并配合ALTERA公司的ACEX系列的EP1K FPGA。EP1K内部包含了多个逻辑模块,这些模块通过WISHBONE总线实现与处理器的交互,从而控制多个UART接口的外部设备。这种设计允许主控芯片能够同时管理4到6个外围设备,极大地提高了系统对外设的控制能力。

在驱动程序设计方面,需要为FPGA中的每个UART接口编写对应的驱动,以使得Linux操作系统能够识别并有效地控制这些扩展的UART端口。驱动程序通常包括初始化、数据发送、接收以及中断处理等功能,确保系统能正确地与外设进行数据交换。

此外,FPGA设计还涉及到了地址映射、数据流控制和错误处理机制,这些都是保证UART扩展总线系统稳定运行的关键要素。通过这样的设计,不仅可以解决单一UART接口的限制,还能提高系统的灵活性和扩展性,以适应不断变化的外设需求。

基于FPGA的UART扩展总线设计提供了一种高效的方法来满足嵌入式系统对外设接口日益增长的需求。通过FPGA的可编程特性,可以灵活地扩展多个UART接口,并通过优化的驱动程序实现与处理器的无缝协作,使得嵌入式系统能够在更复杂的环境中保持高效和可靠。

2022-03-13 上传

2020-11-09 上传

2023-05-31 上传

2023-07-09 上传

2024-04-25 上传

2023-06-30 上传

2023-07-08 上传

2023-07-09 上传

2023-06-10 上传

weixin_38666114

- 粉丝: 7

- 资源: 971

最新资源

- WebLogic集群配置与管理实战指南

- AIX5.3上安装Weblogic 9.2详细步骤

- 面向对象编程模拟试题详解与解析

- Flex+FMS2.0中文教程:开发流媒体应用的实践指南

- PID调节深入解析:从入门到精通

- 数字水印技术:保护版权的新防线

- 8位数码管显示24小时制数字电子钟程序设计

- Mhdd免费版详细使用教程:硬盘检测与坏道屏蔽

- 操作系统期末复习指南:进程、线程与系统调用详解

- Cognos8性能优化指南:软件参数与报表设计调优

- Cognos8开发入门:从Transformer到ReportStudio

- Cisco 6509交换机配置全面指南

- C#入门:XML基础教程与实例解析

- Matlab振动分析详解:从单自由度到6自由度模型

- Eclipse JDT中的ASTParser详解与核心类介绍

- Java程序员必备资源网站大全