ClearNAND闪存:提升系统设计的ECC解决方案

100 浏览量

更新于2024-09-01

收藏 377KB PDF 举报

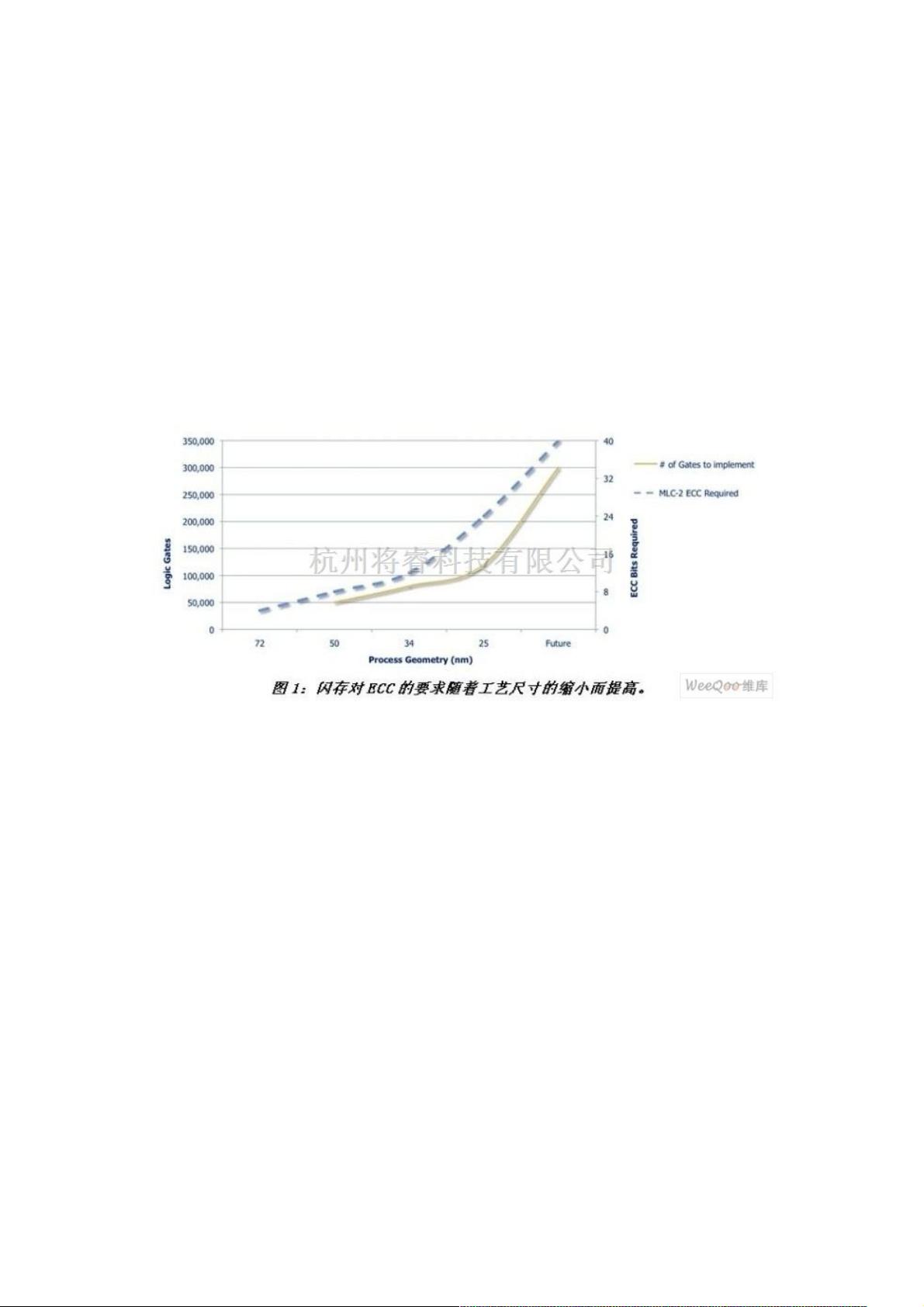

随着信息技术的发展,NAND闪存在现代系统设计中扮演着至关重要的角色,尤其是在数据存储和处理中。早期的NAND闪存通过ECC(错误校验码)技术提高数据可靠性,但随着技术的进步,特别是多层单元(MLC)架构和三比特单元存储的引入,ECC的需求变得更为迫切。随着存储单元尺寸减小,单位存储空间内的电子数量减少,导致位误码率上升,这就需要系统设计者大幅提升ECC纠错能力来保持系统稳定运行。

随着ECC纠错能力要求的提高,实现高精度纠错逻辑的挑战也随之增大。例如,24位ECC和40位ECC分别需要大量的逻辑门来执行复杂的纠错算法,这不仅增加了硬件成本,还提升了系统复杂性。未来的先进ECC可能需要的逻辑门数量甚至可以达到百万级别,这对于硬件设计者来说是一大挑战。

在高性能闪存系统中,多通道NAND闪存的使用成为常态,每个通道都需要独立的ECC逻辑,进一步加大了对ECC资源的需求。以一个10通道的SSD为例,如果每通道采用60位ECC,那么仅仅用于ECC逻辑的逻辑门数就达到了惊人的300万。这不仅考验着系统设计者的集成能力,也影响了整个系统的功耗、面积和成本。

为了应对这些挑战,传统的NAND闪存接口,如异步通信接口,尽管速度有所提升,但仍需适应更高的ECC需求。开放式NAND闪存接口(ONFI)等标准化组织的出现,试图通过简化时序和指令标准来缓解这一问题,但这仍不足以解决日益增长的ECC复杂性。

ClearNAND闪存作为一种新型解决方案,开始受到关注。ClearNAND利用先进的技术和架构优化,能够提供更高效的ECC管理,比如通过降低ECC的复杂性和所需逻辑门的数量,从而减轻系统设计的压力。此外,ClearNAND可能还涉及到新型的数据编码技术,如精简模式或动态ECC,以在保证数据可靠性的前提下,减小存储空间占用和提高整体系统性能。

ClearNAND闪存的引入是系统设计者应对ECC纠错能力需求激增的重要策略,它不仅能够提高存储系统的数据可靠性,还能优化硬件资源使用,降低系统复杂性和成本,从而推动了现代电子系统设计的演进。然而,持续的技术创新和优化仍然是应对未来挑战的关键,包括开发更先进的ECC算法和接口标准,以满足不断增长的系统性能和可靠性需求。

2020-10-24 上传

2020-07-31 上传

2024-09-23 上传

2024-09-23 上传

2024-09-23 上传

2024-09-23 上传

weixin_38621638

- 粉丝: 1

- 资源: 983

最新资源

- ASP.NET数据库高级操作:SQLHelper与数据源控件

- Windows98/2000驱动程序开发指南

- FreeMarker入门到精通教程

- 1800mm冷轧机板形控制性能仿真分析

- 经验模式分解:非平稳信号处理的新突破

- Spring框架3.0官方参考文档:依赖注入与核心模块解析

- 电阻器与电位器详解:类型、命名与应用

- Office技巧大揭秘:Word、Excel、PPT高效操作

- TCS3200D: 可编程色彩光频转换器解析

- 基于TCS230的精准便携式调色仪系统设计详解

- WiMAX与LTE:谁将引领移动宽带互联网?

- SAS-2.1规范草案:串行连接SCSI技术标准

- C#编程学习:手机电子书TXT版

- SQL全效操作指南:数据、控制与程序化

- 单片机复位电路设计与电源干扰处理

- CS5460A单相功率电能芯片:原理、应用与精度分析