"Vitis HLS 用户指南2022年4月版:入门指南和包容性语言宣言"

需积分: 5 19 浏览量

更新于2024-01-18

1

收藏 16.16MB PDF 举报

本文是Vitis高层次综合用户指南UG1399 (v2022.1)的翻译版本,于2022年4月20日发布。翻译版本与英语原文存在差异时以英语原文为准,翻译文本可能不反映最新的英文版本,请查阅最新的英文文档获取最新信息。赛灵思一直致力于创造包容环境,删除非包容性语言,并删除任何可能固化历史偏见的语言。尽管在旧产品中可能会发现非包容性语言,但赛灵思正在努力践行新的使命,以与不断发展的行业标准保持一致。如果需要更多信息,请参阅相关链接。

本文主要分为两个部分:Vitis HLS入门和设计过程浏览内容。第一部分的内容涵盖Vitis HLS的概述,并介绍了Vitis HLS的基本概念、特性和工作流程。第二部分则通过设计过程的浏览,详细介绍了Vitis HLS的具体操作和使用方法。

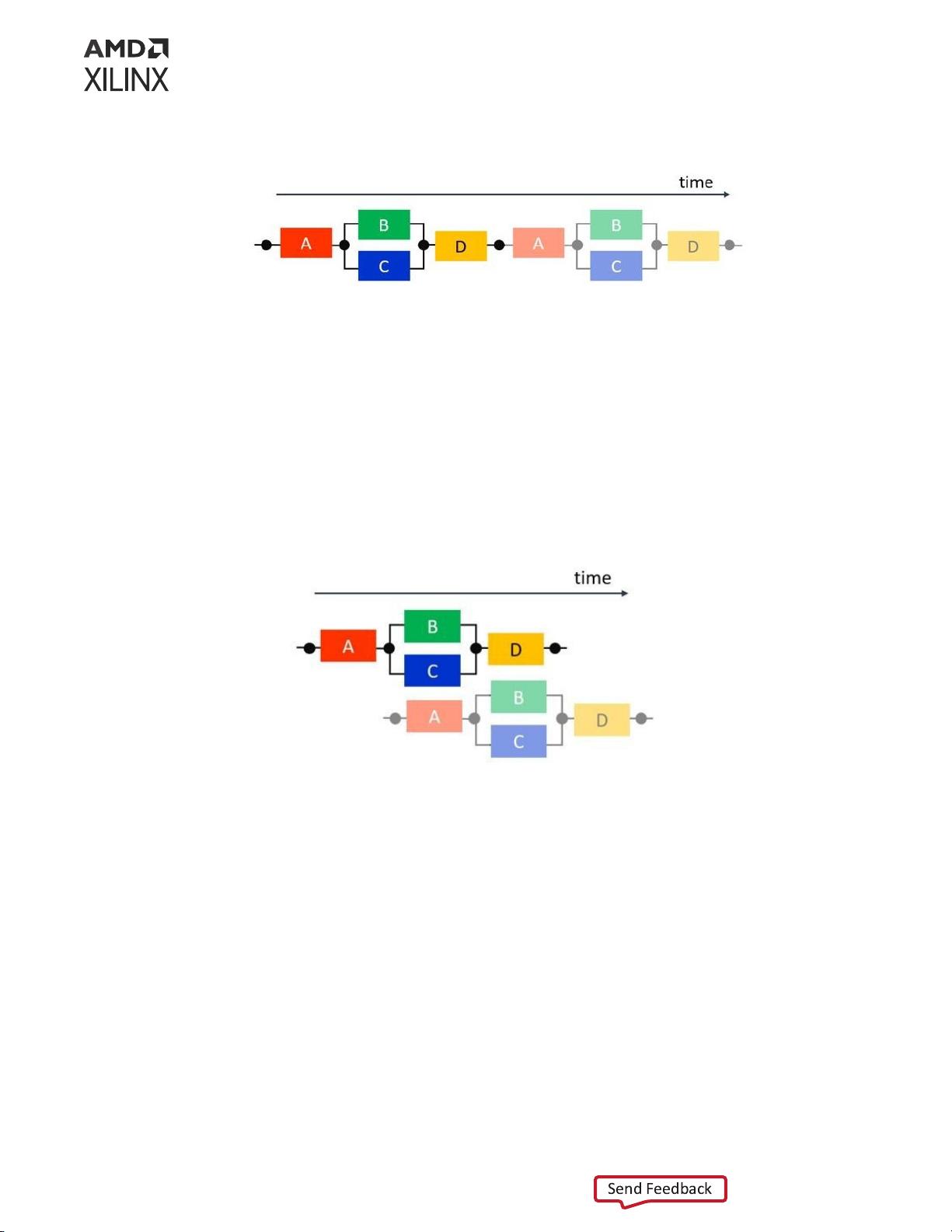

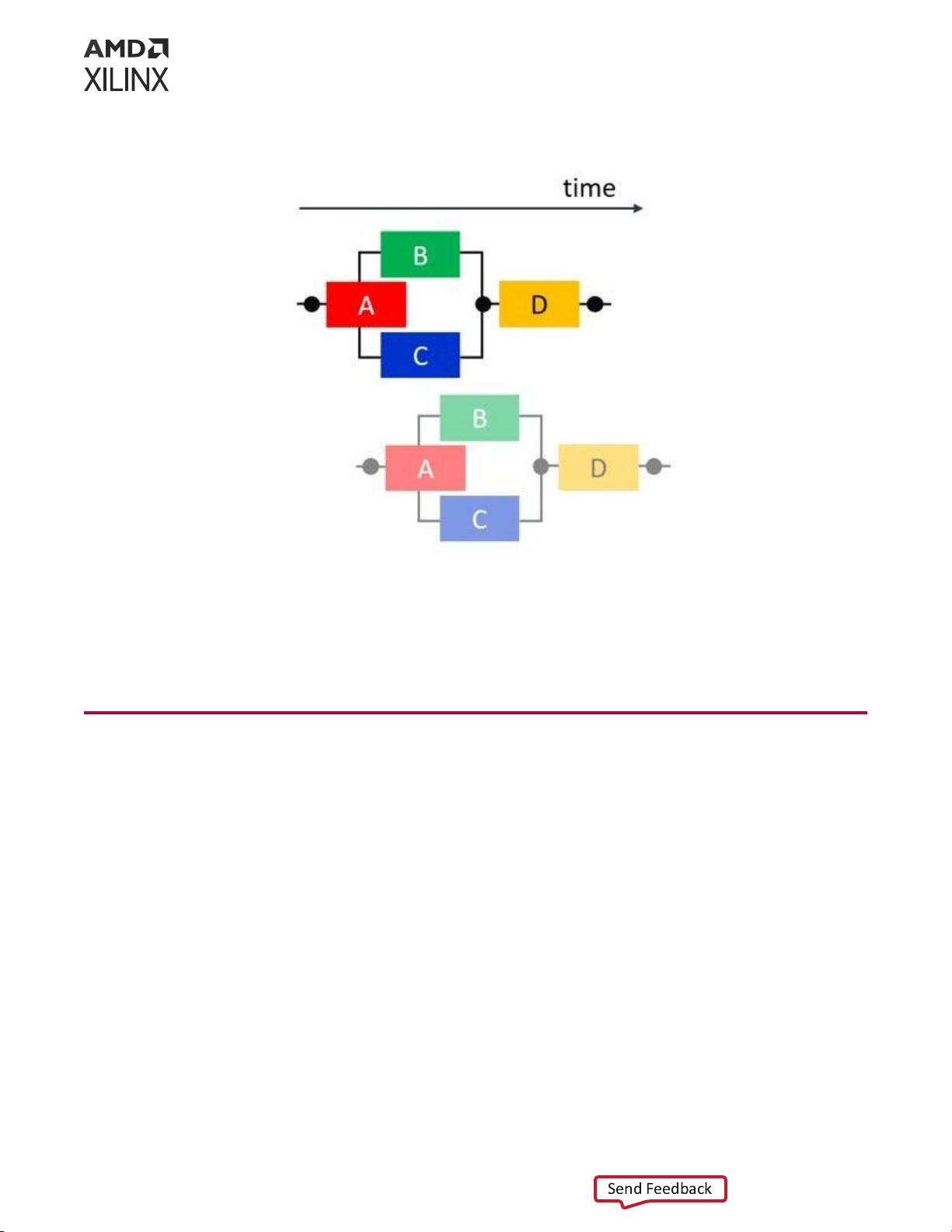

Vitis HLS是一款高层次综合工具,旨在通过C、C++或SystemC等高级语言,快速创建高效的FPGA加速器。它可以自动并行化和优化代码,提高FPGA的性能和效率。Vitis HLS具有用户友好的界面,使得用户可以方便地进行代码优化、调试和验证。

在设计过程中,Vitis HLS提供了丰富的资源库和模板,帮助用户快速创建和调整加速器结构。用户只需按照指南进行简单的配置和设置,即可生成具有高性能、低功耗的FPGA加速器。

同时,Vitis HLS还支持与其他Xilinx工具的集成,包括Vivado Design Suite和SDAccel环境。用户可以通过Vitis HLS生成的IP核,快速将加速器集成到其它项目中,实现快速的原型设计和验证。

除了基本的功能介绍外,本文还包括了大量的案例分析和实际操作指南,帮助用户更好地了解Vitis HLS的具体应用场景和操作方法。通过这些案例,用户可以深入了解Vitis HLS在不同领域的应用,如数字信号处理、机器学习和通信等。同时,本文还提供了丰富的技术支持和资源链接,帮助用户解决在使用Vitis HLS过程中遇到的各种问题。

总的来说,Vitis HLS用户指南UG1399 (v2022.1) 提供了完整的Vitis HLS介绍和详细的操作指南,可以帮助用户快速上手并充分发挥Vitis HLS工具的性能。通过本指南的学习和实践,用户可以更好地应用Vitis HLS工具,加速FPGA开发流程,提高设计效率和产品性能。

203 浏览量

242 浏览量

1061 浏览量

111 浏览量

353 浏览量

268 浏览量

205 浏览量

zaitax2011

- 粉丝: 0

- 资源: 14

最新资源

- RFID 读写器设计

- 射频识别技术及其在室内定位中的应用

- 职业规划设计——网络工程师

- mkl reference manual

- 华为PCB布线规范 -共享

- Fedora_10_Installation_Guide_Chinese

- virtex-5 用户手册(中文)

- css+div 用于页面布局

- struts1.x配置

- AutoCAD形文件的自动生成

- MATLAB 绘图的PPt

- 微机实验 汇编语言 bcd

- Architecture Independent For Wireless Sensor.pdf

- Linux Command Directory

- 经典路由器配置实例(案例分析)

- openmp 编程指南