Xilinx Scaler IP UG009:卷积处理与时钟计算详解

需积分: 10 149 浏览量

更新于2024-07-15

收藏 2.4MB PPTX 举报

UG009是Xilinx提供的关于Scalable IP(可缩放IP)的用户指南,主要关注于Resizer模块的详细介绍。该文档涵盖了以下几个关键知识点:

1. **相位偏移与滤波器权重**:

当使用不同的缩放因子进行图像放大或缩小时,输出像素与输入图像的重叠部分可能存在相位偏移。为了正确处理这种偏移,相关的滤波器权重也需要相应调整,以确保图像质量。

2. **表格与计算**:

缩放因子的变化会影响内部的算法表,这些表是通过计算得出的,用于存储处理图像缩放所需的权重数据。

3. **硬件卷积原理**:

硬件实现通常采用一维的序列卷积,对图像进行两次处理,可以按垂直或水平方向优先。这意味着算法不能直接处理二维卷积,而是需要分解成两步处理。

4. **valid信号管理**:

valid信号在数据传输中起着重要作用,它控制数据的有效性。设置valid为1表示数据可用,但如果硬件未准备好接收,数据可能无法传输。ready信号则指示硬件是否可以接收新数据,一旦变为可用,valid信号可以立即激活。

5. **SOF和EOF信号**:

SOF(Start of Frame)和EOF(End of Frame)分别标记帧的开始和结束,它们需要与帧的交易周期同步。SOF可以在VBlank期间拉高,但必须与下一帧的第一个像素交易周期重叠,而EOF则需与最后一像素的交易周期一致,以便与下一个时钟周期无缝衔接。

6. **时钟计算**:

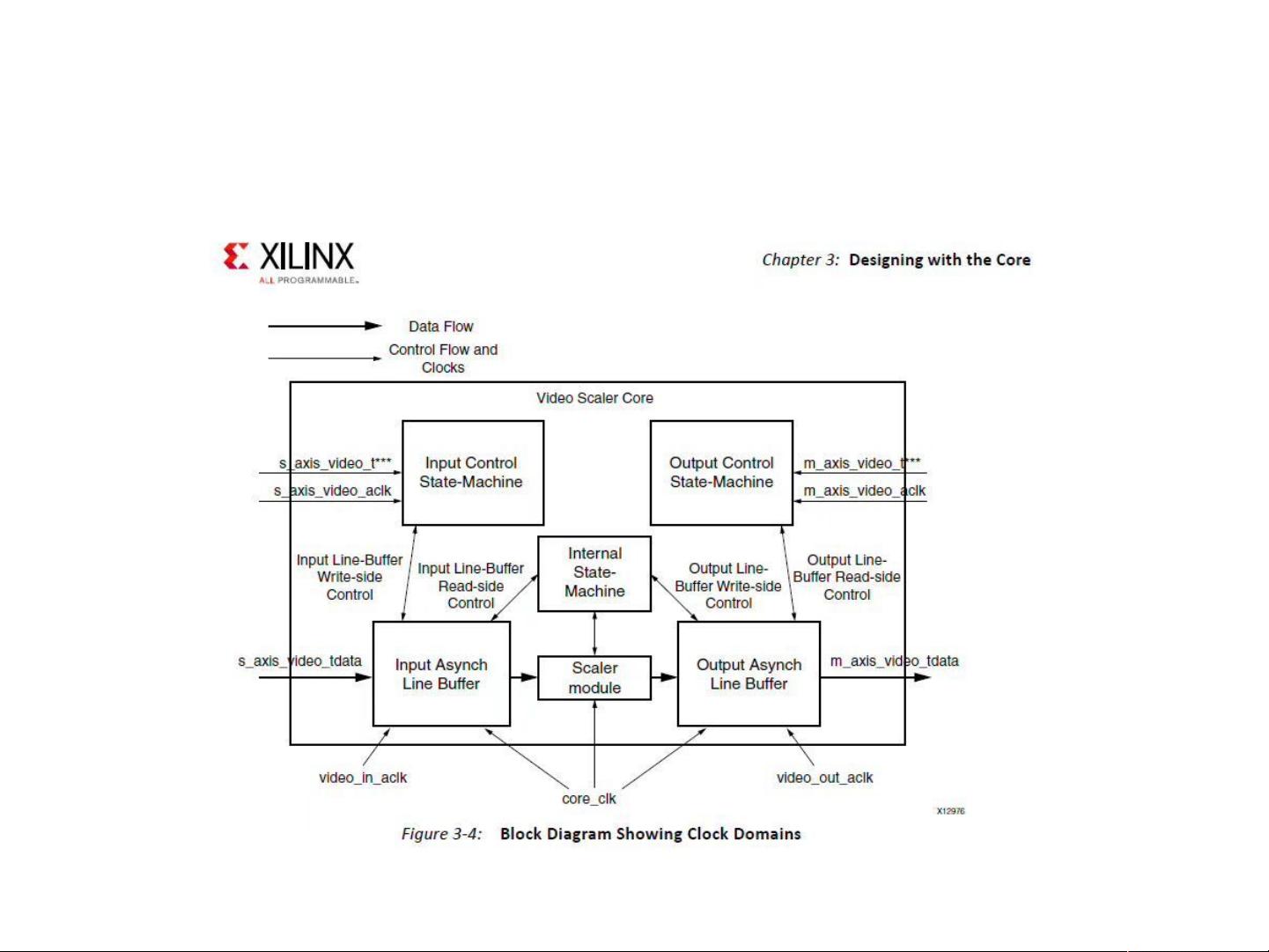

在live-mode下,Scaler的设计要考虑输入时钟(in_clk)的影响,它取决于图像分辨率和刷新率。Scalable IP的核心时钟(core_clk)和输出时钟(out_clk)都需要确保在输入数据更新前完成计算并写入输出缓冲区,同时,out_clk还要保证输出数据能在被下一级接收前从outputfifo输出。

7. **连续数据流处理**:

输入数据连续不断地填充到input fifo中,Scaler在不改变刷新率的前提下执行缩放操作。核心时钟和输出时钟的频率要根据输入时钟调整,以保持数据处理的稳定性和帧同步。

这些知识点展示了如何在Xilinx Scalable IP的Resizer模块中进行高效的图像缩放处理,以及如何管理时钟和信号以确保数据传输的准确性。理解这些细节对于设计和优化基于Xilinx平台的图像处理系统至关重要。

2021-09-21 上传

2023-12-20 上传

2023-02-06 上传

flashks

- 粉丝: 0

- 资源: 1

最新资源

- php-microservice-cqrs-es:使用CQRS + Event SourcingPHP Microservice样板

- xMovingMap:适用于X-Plane的Android移动地图

- layout_style-it-up

- gitcommands:有用的 Git 命令

- ArpSpoof

- wetch-frontend:TFM UOC

- 毕业设计&课设-行人检测系统的MatLab代码.zip

- 睡眠教学助手:OS项目:使用互斥锁和信号灯的睡眠教学助手

- liczby_pierwsze

- Spider-Programmes:Here is a collection of my web crawler repositories.(汇聚了我的爬虫程序仓库)

- keystone:梯形飞地(QEMU + HiFive Unleashed)

- lumen-api-query-parser:基于laravel流明框架的REST-API查询解析器

- reticulate:R与Python的接口

- 客户端-服务器-聊天-对等之间:套接字编程的C#GUI应用程序,两个客户端通过同一ip和端口进行双方聊天

- LogiKM:一站式Apache Kafka集群指标监控与运维管控平台

- 毕业设计&课设-基于Matlab的物体轨迹仿真.zip