Xilinx Virtex-5用户手册中文版

需积分: 10 110 浏览量

更新于2024-07-25

收藏 7.69MB PDF 举报

"Virtex-5用户指南-UG190中文版,Xilinx公司发布,用于指导用户在Virtex-5 FPGA上进行设计开发。文档包含了详细的技术信息和知识产权条款。"

Xilinx的Virtex-5系列是基于SRA (SystemReady Architecture) 的高性能FPGA,广泛应用于各种嵌入式系统、通信、计算和信号处理应用。该用户指南,即UG190,是专为开发者提供的一份详尽参考资料,旨在帮助他们充分利用Virtex-5 FPGA的特性并顺利进行设计。

在Virtex-5 FPGA中,主要包含以下几个关键知识点:

1. **逻辑单元(Logic Cells)**:Virtex-5系列FPGA的核心是大量的可编程逻辑单元,它们可以配置为各种逻辑门电路,如与或非门、触发器等,以实现用户的设计需求。

2. **查找表(LUTs)**:每个逻辑单元通常包括4输入查找表(LUT),这些LUTs允许实现复杂的逻辑函数,提高了设计的灵活性。

3. **分布式存储器(Block RAMs)**:Virtex-5提供了内嵌的分布式RAM资源,可用于创建片上存储器,如数据缓冲区或寄存器文件,这对于高性能数据处理至关重要。

4. **专用硬核模块(Hard IP Blocks)**:包括浮点运算单元、串行高级传输接口(Serial ATA)、千兆位以太网MAC、PCI Express等,这些预定义的功能块可以加速特定功能的实现。

5. **时钟管理(Clock Management)**:Virtex-5支持多种时钟管理技术,如PLL(锁相环)和DLL(延迟锁定环),确保在整个设计中的时钟同步和时序优化。

6. **I/O接口(IOBs)**:输入/输出缓冲区(IOBs)提供了灵活的接口,以适应不同的电压标准和速度等级,支持高速接口协议,如LVDS(低压差分信号)。

7. **功耗管理**:Virtex-5具有低功耗特性,如动态功率调整和时钟分区,有助于在保持性能的同时降低整体功耗。

8. **布线资源**:内部的互连网络使得逻辑单元、存储器块和I/O之间能够高效通信,实现大规模的逻辑设计。

9. **设计流程**:Xilinx提供了一整套设计工具,如ISE(Integrated Software Environment)、PlanAhead和Synplify等,用于设计输入、综合、布局布线和仿真。

10. **知识产权(IP)核**:Xilinx提供了一系列预先验证的IP核,例如数字信号处理器(DSP48E)和嵌入式微处理器,可以直接集成到设计中,加速开发进程。

用户在使用UG190时,不仅要注意技术细节,还需要遵循文档中提到的知识产权条款。Xilinx强调未经许可,不得复制、分发或以其他形式使用设计内容,同时,使用设计可能涉及的版权、商标、隐私权和公开权等问题,由用户自行负责。Xilinx保留随时对设计进行修改的权利,以满足技术发展的需求。

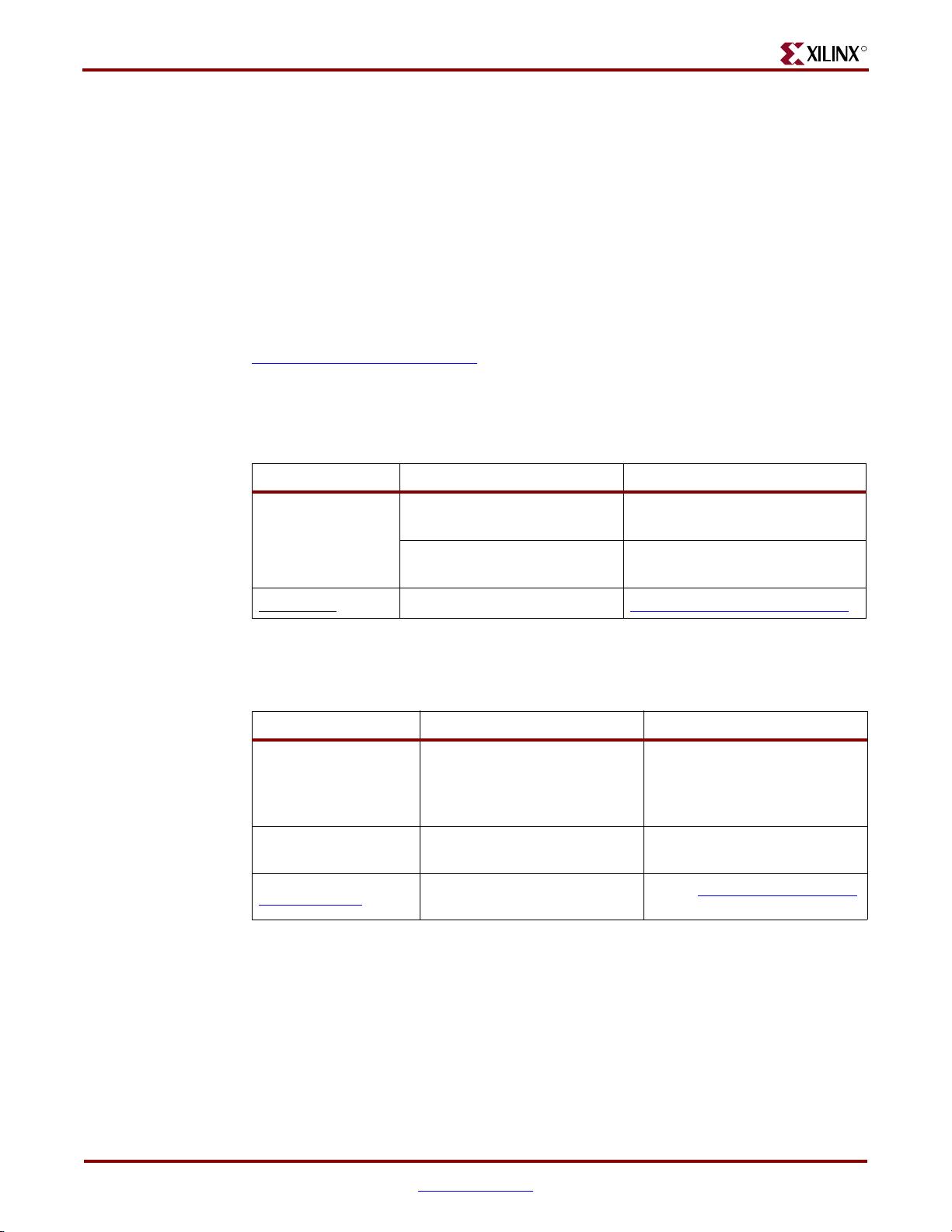

2009-12-29 上传

2022-08-03 上传

2022-08-03 上传

点击了解资源详情

点击了解资源详情

2019-05-21 上传

Dereklee0302

- 粉丝: 0

- 资源: 4

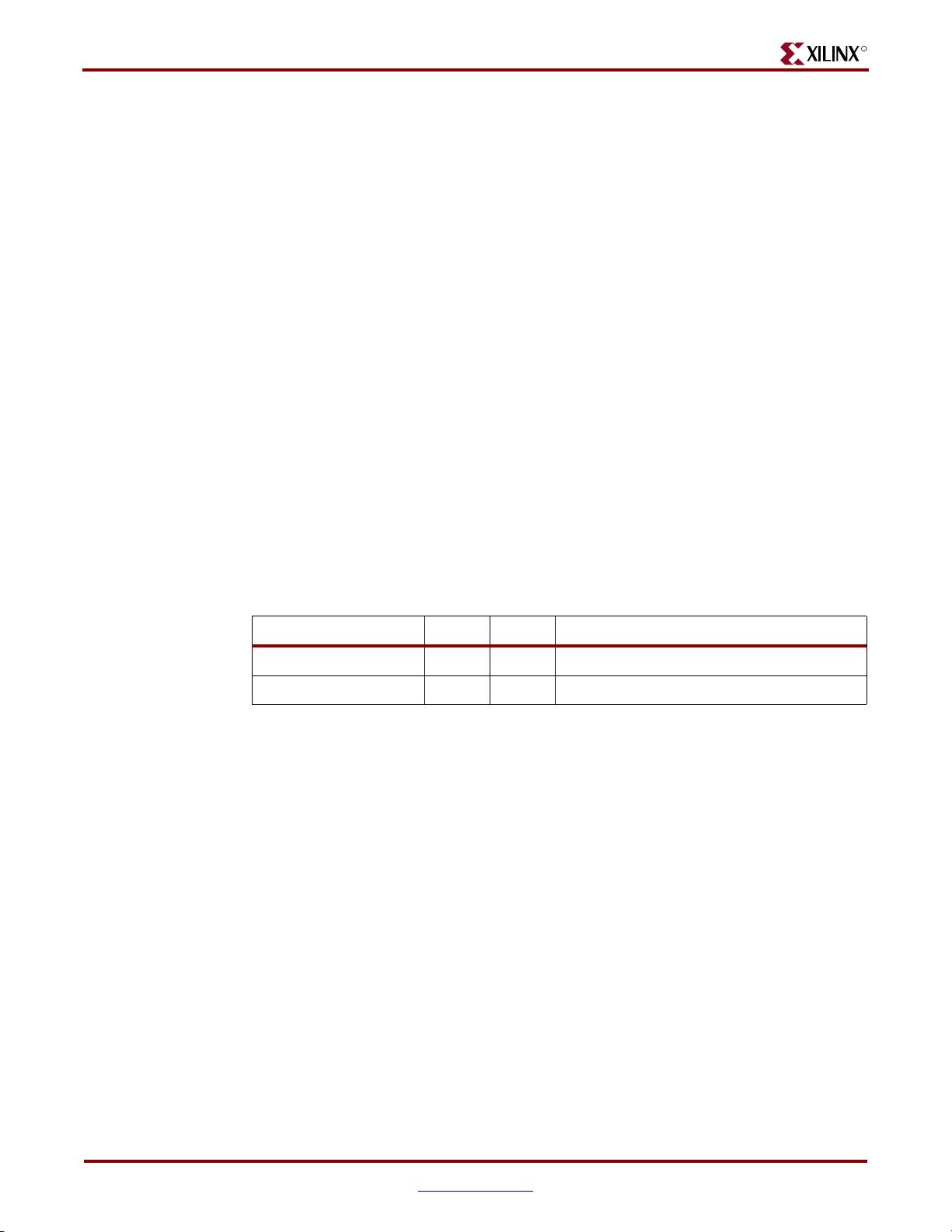

最新资源

- vue-element-Admin-demo:vue-element-Admin框架源代码

- SCOPE:用于在 SEER 中重新编码死因 (COD) 的实用程序:此 SCOPE 实用程序用于重新编码 SEER 中观察到的死亡变量的死因。-matlab开发

- [上传下载]Labs.net.cn简单图片上传系统 Beta1_upload.rar

- JunioResende

- 捐赠网络应用

- xyzsh:交互式外壳和文本处理工具

- Pingle:Web Ping工具,Web工具,Ping,站点-开源

- th2wc-blueprints:从 ThemeHybrid 和 WooCommerce 轻松开始使用主题的蓝图

- sourcecode-write:每2周对一个热门的前端框架进行源码分析,并画出思维导图

- 如何静音来电铃声

- 安卓幻影WIFI_3.0 适配安卓8.0以上.txt打包整理.zip

- A_star_Udacity:Udacity的A *任务1

- hash_tree,怎样阅读c语言源码,c语言

- 仿健客网手机wap药店网站模板_网站开发模板含源代码(css+html+js+图样).zip

- SCOPE:计算阳性淋巴结百分比的实用程序:该程序删除检查的淋巴结为零的病例并计算阳性 LN 密度。-matlab开发

- redux-ts:react + redux +打字稿