"信号与变量异同:VHDL语言描述语句的区别和应用范围及操作特点"

需积分: 50 193 浏览量

更新于2024-01-13

收藏 983KB PPT 举报

信号和变量是VHDL语言中常用的描述语句。它们有一些相同点,也有一些不同点。在声明范围方面,信号可以在ENTITY、ARCHITECTURE和PACKAGE中声明,而变量只能在顺序语句(如PROCESS、子程序)中声明。信号和变量的作用也有所不同,信号用于动态数值传递,可以存储运算中间结果,而变量只能用于存储运算中间结果。在使用范围方面,信号可以是全局的(sig)或局部的,而变量只能是局部的(var)。此外,变量的结果只能通过信号传递到外部。

信号和变量在动作特点上也有所区别。变量的更新是立即生效的,而信号在PROCESS执行完毕后才会生效。这意味着变量可以在同一个进程中实时更新,而信号的变化只在进程执行完毕后才会被触发(允许多驱动源,但只有最后一个有效)。在操作符方面,信号使用“<=”进行赋值操作,而变量使用“:=”进行赋值操作。

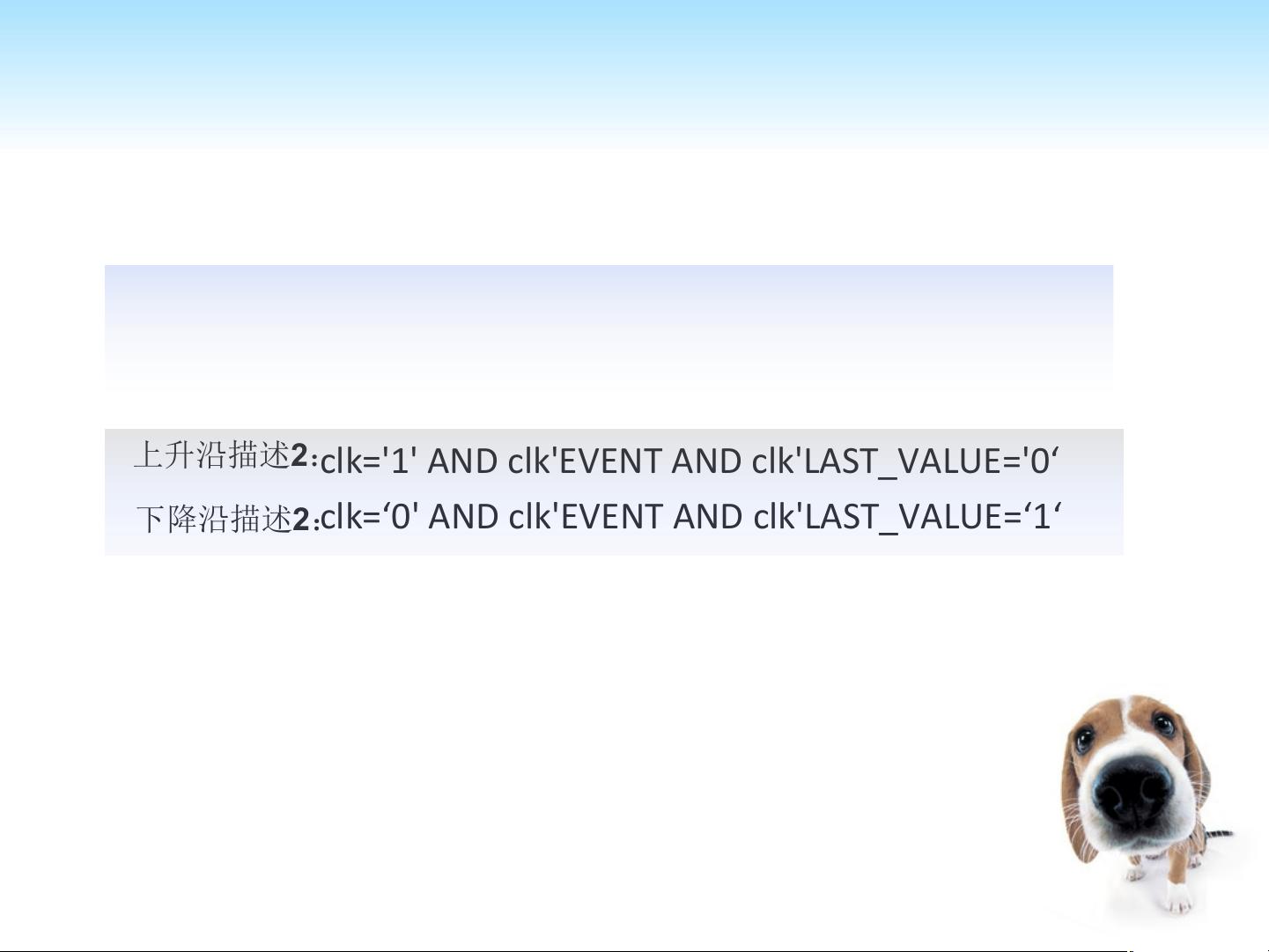

VHDL语言中的语句可以按照功能和执行方式进行分类。按照功能分类,有赋值语句、数据流控制语句(顺序和并行)、模块化设计语句和仿真语句。赋值语句主要用于给变量或信号赋值。数据流控制语句包括Case...when和If...else等,用于根据条件执行不同的语句块。模块化设计语句用于描述模块之间的关系和结构,如process、component、generate、block和for...loop等。仿真语句用于控制仿真过程中的等待和时钟变化。

语句的执行方式特点也可以分为并行和顺序两种。并行语句的执行顺序与书写顺序无关,适用于进程语句外部的语句。并行语句对应于各自独立运行的逻辑电路。顺序语句则按照语句的书写顺序执行,适用于进程语句内部的语句。顺序语句主要用于控制逻辑电路中的顺序执行。

总结起来,信号和变量是VHDL语言中常用的描述语句。它们在声明范围、作用、使用范围、动作特点和操作符等方面都有所不同。此外,VHDL语言中的语句可以按照功能和执行方式进行分类,其中并行语句和顺序语句是常见的两种执行方式。对于VHDL语言的设计和编程,了解信号和变量的特点以及各种语句的使用方法是非常重要的。

2020-08-03 上传

2021-08-11 上传

2010-08-17 上传

2013-06-03 上传

2021-08-11 上传

2022-11-07 上传

雪蔻

- 粉丝: 28

- 资源: 2万+

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查