5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

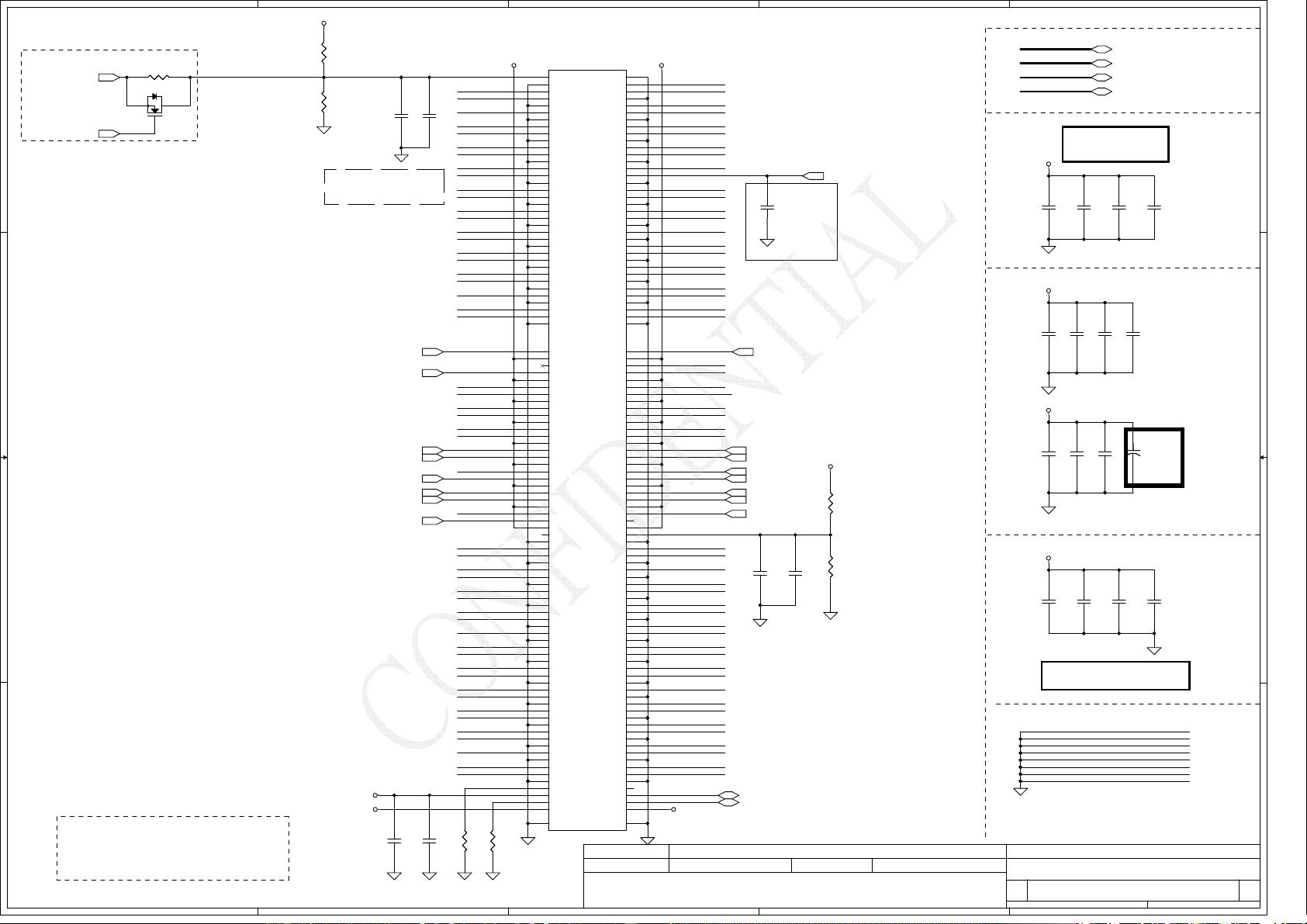

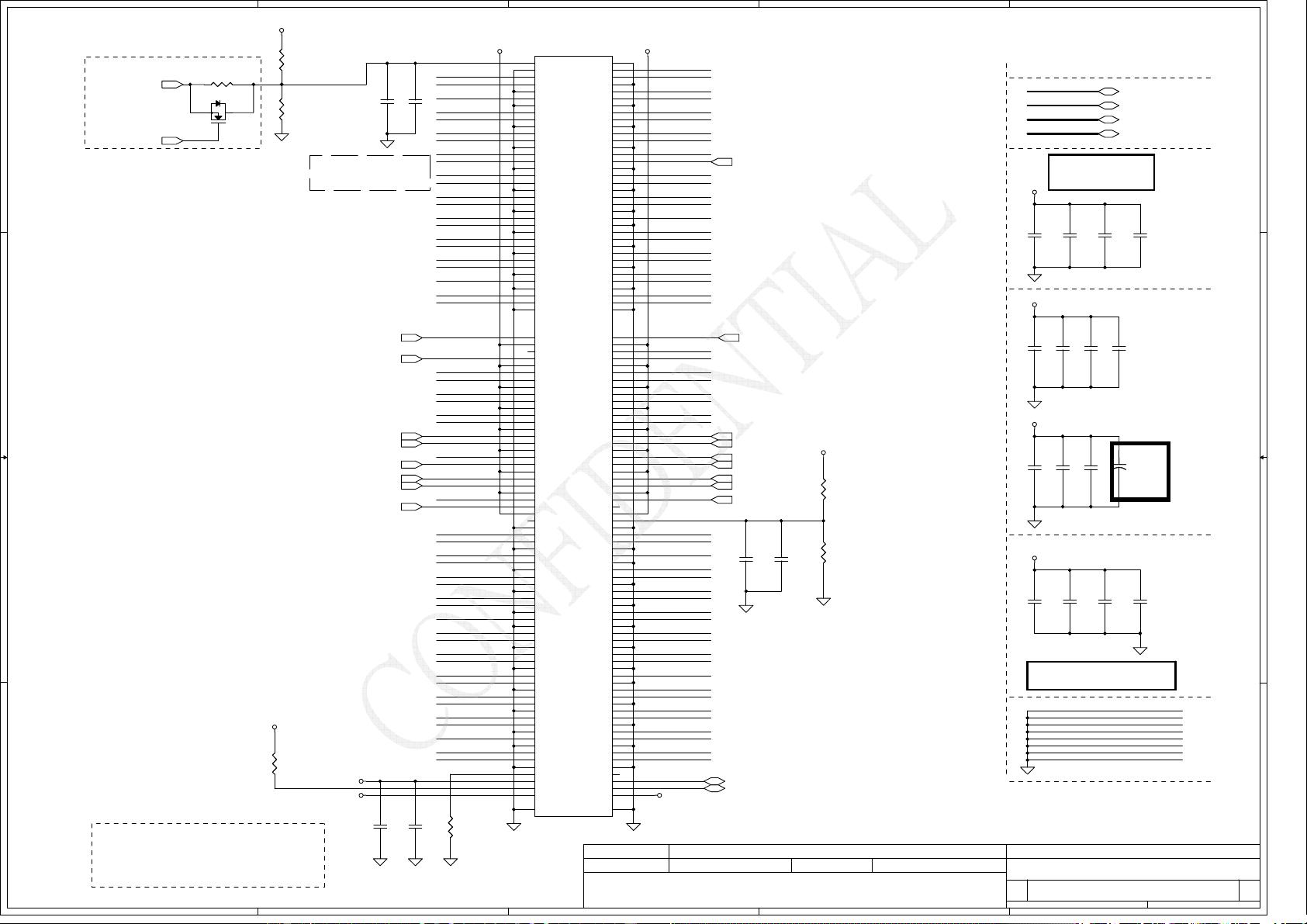

PCH_RTCX1

PCH_RTCX2

PCH_RTCX1

PCH_RTCRST#

SM_INTRUDER#

PCH_INTVRMEN

SM_INTRUDER#

PCH_SPKR

PCH_SPI_MOSI

PCH_SPI_MISO

PCH_SPI_CS0#_1

PCH_JTAG_TCK

PCH_SATALED#

PCH_SRTCRST#

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

HDA_SYNC_PCH

HDA_RST_PCH#

HDA_SDIN0

HDA_SDOUT_PCH

PCH_RTCX2

HDA_BITCLK_PCH

LPC_AD2

LPC_FRAME#

LPC_AD0

LPC_AD3

LPC_AD1

SERIRQ

PCH_GPIO19

SATA_COMP

RBIAS_SATA3

SATA3_COMP

HDA_BITCLK_PCH

HDA_RST_PCH#

HDA_SDOUT_PCH

PCH_INTVRMEN

PCH_SPKR

HDA_SDOUT_PCH

HDA_SYNC_PCH

HDA_SYNC_PCH_R

PCH_SPI_CLK_1

PCH_SPI_MOSI_1

PCH_SPI_MISO_1

SGEN#

SERIRQ

PCH_SATALED#

PCH_GPIO19

+RTCBATT_R

PCH_SPI_MISO_1

PCH_SPI_CS0#_1

PCH_SPI_CLK_1

PCH_SPI_MOSI_1

SPI_WP1#

SPI_HOLD1#

SPI_WP1#

SPI_HOLD1#

PCH_SPI_CLK_1

SGEN#

HDA_SYNC_PCHHDA_SYNC_PCH_R

PCH_SPI_CLK_2

PCH_SPI_CLK

PCH_SPI_CS0#_2

PCH_SPI_MOSI_2

PCH_SPI_MISO_2

SPI_HOLD2#

SPI_WP2#

PCH_SPI_CS0#_2

PCH_SPI_CLK_2

PCH_SPI_MOSI_2

PCH_SPI_MISO_2

SPI_WP2#

SPI_HOLD2#

PCH_SPI_CLK_2

PCH_SPI_VCC

PCH_GPIO23

PCH_GPIO23

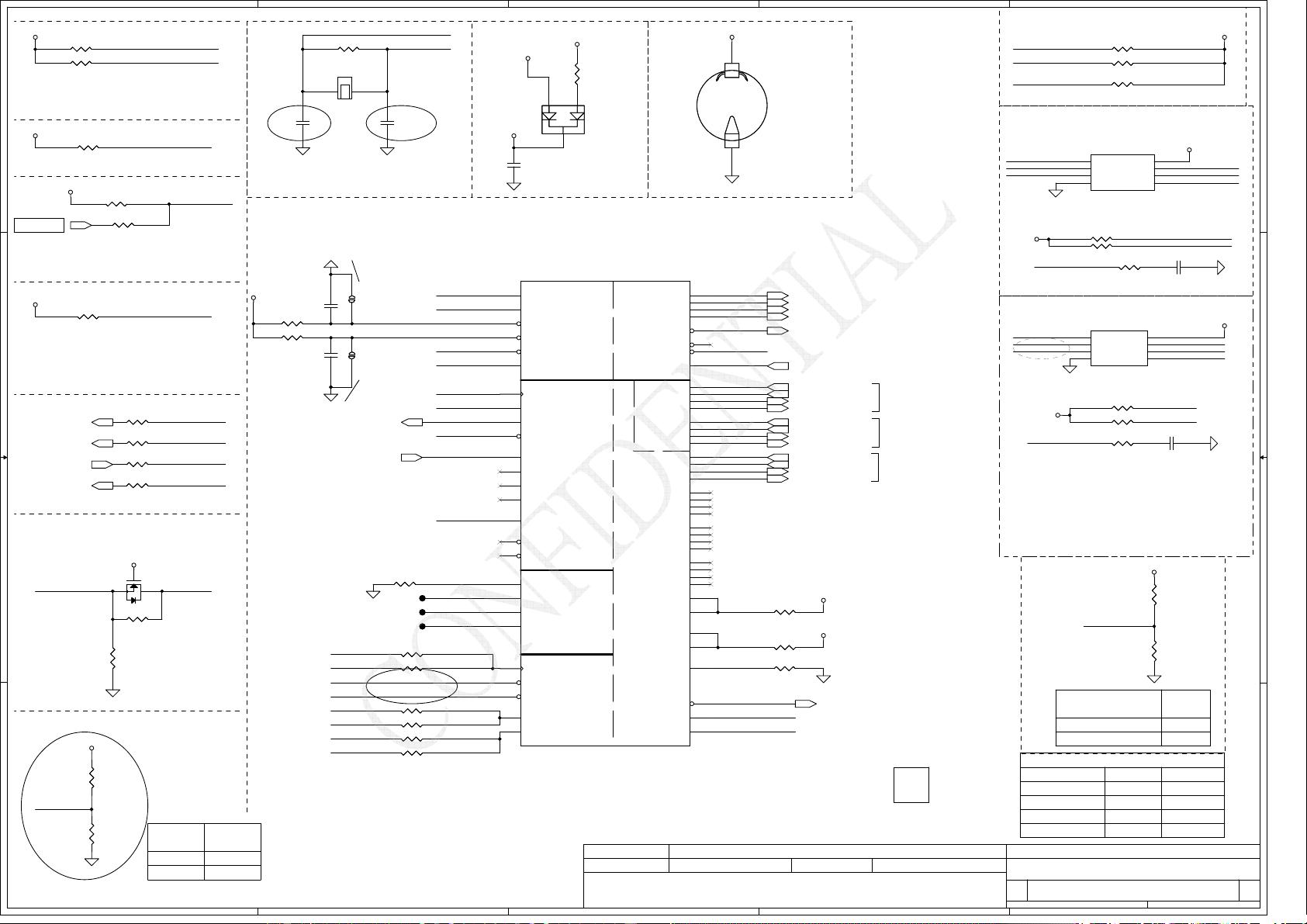

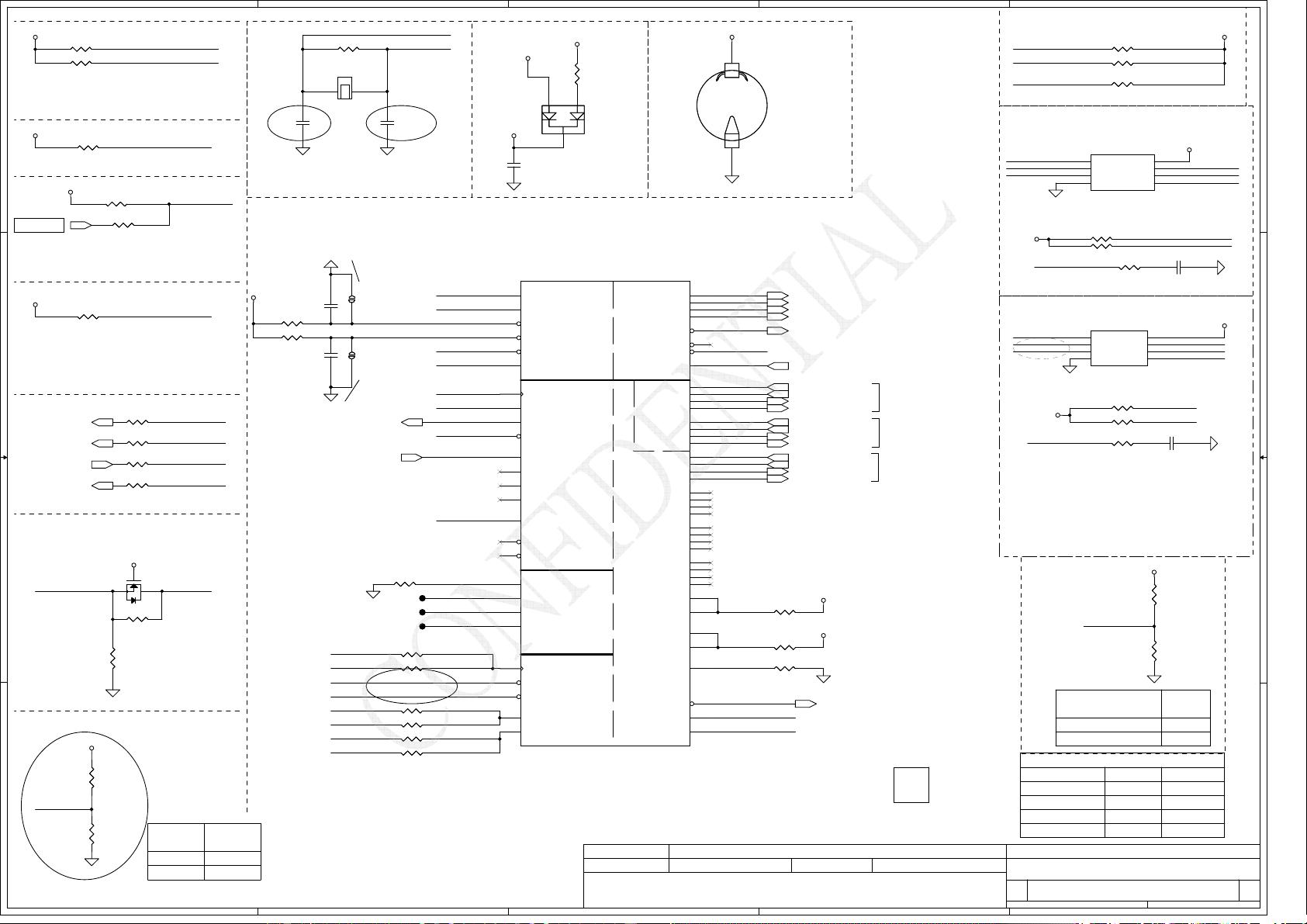

PCH_SPKR<42>

HDA_SDIN0<42>

SERIRQ <40>

SATA_PRX_DTX_P0 <34>

SATA_PTX_DRX_N0 <34>

SATA_PTX_DRX_P0 <34>

SATA_PRX_DTX_N0 <34>

LPC_AD0 <40>

LPC_AD1 <40>

LPC_AD2 <40>

LPC_AD3 <40>

LPC_FRAME# <40>

HDA_SYNC_AUDIO<42>

HDA_SDOUT_AUDIO<42>

HDA_RST_AUDIO#<42>

HDA_BITCLK_AUDIO<42>

PCH_SATALED# <41>

ME_EN<40>

SATA_PRX_DTX_P2 <34>

SATA_PTX_DRX_N2 <34>

SATA_PTX_DRX_P2 <34>

SATA_PRX_DTX_N2 <34>

SATA_PRX_DTX_P1 <37>

SATA_PTX_DRX_N1 <37>

SATA_PTX_DRX_P1 <37>

SATA_PRX_DTX_N1 <37>

+RTCVCC

+RTCVCC

+1.05VS_VTT

+1.05VS_VTT

+3VS

+3VALW_PCH

+3VALW_PCH

+3VS

+CHGRTC

+RTCVCC

+RTCBATT

+3VS

+3VS

+3VS

+RTCBATT

+3VS

+3VS

+3VS

+3VS

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

4019ID

C

SCHEMATIC,MB A7912

Custom

13 63Friday, February 10, 2012

2011/06/02 2012/06/02

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

4019ID

C

SCHEMATIC,MB A7912

Custom

13 63Friday, February 10, 2012

2011/06/02 2012/06/02

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

4019ID

C

SCHEMATIC,MB A7912

Custom

13 63Friday, February 10, 2012

2011/06/02 2012/06/02

SRTCRST close RAM door

RTCRST close RAM door

HDD

Compal Electronics, Inc.

H:Integrated VRM enable

L:Integrated VRM disable

INTVRMEN

*

LOW= Disable (Default)

HIGH= Enable ( No Reboot )

*

*

Low = Disabled (Default)

High = Enabled [Flash Descriptor Security Overide]

This signal has a weak internal pull-down

On Die PLL VR Select is supplied by

1.5V when smapled high

1.8V when sampled low

Needs to be pulled High for Huron River platfrom

*

(INTVRMEN should always be pull high.)

ME debug mode,this signal has a weak internal PD

HDA_SDO

as Capella ME override (GPIO33)

Boot BIOS GPIO19

0

1

SPI

-

GPIO51

Reserved

LPC

Boot BIOS Strap

1

1

0

*

0

1

0

ODD

20mil

20mil

This part had been re-modified

be careful,if link symbol!!

SPI ROM FOR ME (4MB)

Footprint 200mil

Rserve the 2M ROM for Win8

GPIO21

0

1*

Switchable GPU

Non-Switchable

SGEN#

Prevent back drive issue.

MSATA

Modify R02

R02 Modify

Modify R03

Co-lay NPCE885N

R04 modify

R04 modify

Modify R04

Delete Co-lay NPCE885N

GPIO23

0

1

USB2.0

USB3.0

USB_config

modify on 7912 V0.3

R555

33_0402_5%

R555

33_0402_5%

1 2

R681 33_0402_5%R681 33_0402_5%

1 2

R667 3.3K_0402_5%R667 3.3K_0402_5%

1 2

R539 1K_0402_5%R539 1K_0402_5%

12

U33

BD82HM77 QPRG C1 BGA 989P

HM77@

SA00005AG00

U33

BD82HM77 QPRG C1 BGA 989P

HM77@

SA00005AG00

G

D

S

Q36

S TR SSM3K7002F 1N SC59-3

G

D

S

Q36

S TR SSM3K7002F 1N SC59-3

2

13

R557

0_0402_5%

R557

0_0402_5%

12

R243 20K_0402_1%R243 20K_0402_1%

1 2

R275 10K_0402_5%R275 10K_0402_5%

12

R654 3.3K_0402_5%R654 3.3K_0402_5%

1 2

R585 330K_0402_5%R585 330K_0402_5%

1 2

R624 4.7K_0402_5%R624 4.7K_0402_5%

1 2

R2092

20K_0402_1%

PUSB2@

R2092

20K_0402_1%

PUSB2@

1 2

C360

1U_0603_10V6K

C360

1U_0603_10V6K

1

2

R640 10K_0402_5%R640 10K_0402_5%

12

JBATT1

SUYIN_060003HA002G202ZLCONN@

JBATT1

SUYIN_060003HA002G202ZLCONN@

+

1

-

2

U36

32M W25Q32BVSSIG_SO8

U36

32M W25Q32BVSSIG_SO8

CS#

1

SO/SIO1

2

WP#

3

GND

4

VCC

8

HOLD#

7

SCLK

6

SI/SIO0

5

R544

33_0402_5%

R544

33_0402_5%

1 2

R294 1K_0402_5%@R294 1K_0402_5%@

1 2

R568 10M_0402_5%R568 10M_0402_5%

1 2

U42

MX25L1606EM2I-12G_SO8

WIN8@U42

MX25L1606EM2I-12G_SO8

WIN8@

CS#

1

SO

2

WP#

3

GND

4

VCC

8

HOLD#

7

SCLK

6

SI

5

R567 1M_0402_5%R567 1M_0402_5%

1 2

R734 33_0402_5%

WIN8@

R734 33_0402_5%

WIN8@

12

C2049

33P_0402_50V8K

@ C2049

33P_0402_50V8K

@

C682

15P_0402_50V8J

C682

15P_0402_50V8J

1

2

D13

CHN202UPT_SC70-3

D13

CHN202UPT_SC70-3

1

2

3

R260

37.4_0402_1%

R260

37.4_0402_1%

1 2

R2050 33_0402_5%

WIN8@

R2050 33_0402_5%

WIN8@

1 2

JCMOS1

SHORT PADS

@

JCMOS1

SHORT PADS

@

12

R248 20K_0402_1%R248 20K_0402_1%

1 2

R866

22_0402_5%

@

R866

22_0402_5%

@

1 2

R2048

22_0402_5%

@ R2048

22_0402_5%

@

1 2

R674

51_0402_5%

@R674

51_0402_5%

@

12

T76

@

PAD T76

@

PAD

C471

0.1U_0402_16V4Z

C471

0.1U_0402_16V4Z

1

2

R556

1K_0402_5%

@

R556

1K_0402_5%

@

12

R625

750_0402_1%

R625

750_0402_1%

1 2

C893

33P_0402_50V8K

@

C893

33P_0402_50V8K

@

C686

15P_0402_50V8J

C686

15P_0402_50V8J

1

2

T77

@

PAD T77

@

PAD

R241

49.9_0402_1%

R241

49.9_0402_1%

1 2

T75

@

PAD T75

@

PAD

RTCIHDA

SATA

LPC

SPI

JTAG

SATA 6G

U33A

COUGARPOINT_FCBGA989~D

SA00004EEY0

HM65@

RTCIHDA

SATA

LPC

SPI

JTAG

SATA 6G

U33A

COUGARPOINT_FCBGA989~D

SA00004EEY0

HM65@

RTCX1

A20

RTCX2

C20

INTVRMEN

C17

INTRUDER#

K22

HDA_BCLK

N34

HDA_SYNC

L34

HDA_RST#

K34

HDA_SDIN0

E34

HDA_SDIN1

G34

HDA_SDIN2

C34

HDA_SDO

A36

SATALED#

P3

FWH0 / LAD0

C38

FWH1 / LAD1

A38

FWH2 / LAD2

B37

FWH3 / LAD3

C37

LDRQ1# / GPIO23

K36

FWH4 / LFRAME#

D36

LDRQ0#

E36

RTCRST#

D20

HDA_SDIN3

A34

HDA_DOCK_EN# / GPIO33

C36

HDA_DOCK_RST# / GPIO13

N32

SRTCRST#

G22

SATA0RXN

AM3

SATA0RXP

AM1

SATA0TXN

AP7

SATA0TXP

AP5

SATA1RXN

AM10

SATA1RXP

AM8

SATA1TXN

AP11

SATA1TXP

AP10

SATA2RXN

AD7

SATA2RXP

AD5

SATA2TXN

AH5

SATA2TXP

AH4

SATA3RXN

AB8

SATA3RXP

AB10

SATA3TXN

AF3

SATA3TXP

AF1

SATA4RXN

Y7

SATA4RXP

Y5

SATA4TXN

AD3

SATA4TXP

AD1

SATA5RXN

Y3

SATA5RXP

Y1

SATA5TXN

AB3

SATA5TXP

AB1

SATAICOMPI

Y10

SPI_CLK

T3

SPI_CS0#

Y14

SPI_CS1#

T1

SPI_MOSI

V4

SPI_MISO

U3

SATA0GP / GPIO21

V14

SATA1GP / GPIO19

P1

JTAG_TCK

J3

JTAG_TMS

H7

JTAG_TDI

K5

JTAG_TDO

H1

SERIRQ

V5

SPKR

T10

SATAICOMPO

Y11

SATA3COMPI

AB13

SATA3RCOMPO

AB12

SATA3RBIAS

AH1

R733 33_0402_5%

WIN8@

R733 33_0402_5%

WIN8@

12

R259

10K_0402_5%

R259

10K_0402_5%

12

JME1

SHORT PADS

@

JME1

SHORT PADS

@

12

R704

3.3K_0402_5%

WIN8@R704

3.3K_0402_5%

WIN8@

1 2

R542

33_0402_5%

R542

33_0402_5%

1 2

R792

1M_0402_5%

R792

1M_0402_5%

12

R258

10K_0402_5%

@

R258

10K_0402_5%

@

12

C356

1U_0603_10V6K

C356

1U_0603_10V6K

1

2

R545

33_0402_5%

R545

33_0402_5%

1 2

R684 33_0402_5%R684 33_0402_5%

1 2

R375

1K_0402_5%

R375

1K_0402_5%

1 2

R540

0_0402_5%

@

R540

0_0402_5%

@

1 2

Y3

32.768KHZ_12.5PF_FC-135

Y3

32.768KHZ_12.5PF_FC-135

1 2

R2128

20K_0402_1%

PUSB3@

R2128

20K_0402_1%

PUSB3@

1 2

R703

3.3K_0402_5%

WIN8@R703

3.3K_0402_5%

WIN8@

1 2

R652 33_0402_5%R652 33_0402_5%

1 2