帧同步搜索电路设计与仿真:容错与假同步过滤

需积分: 9 149 浏览量

更新于2024-09-17

收藏 211KB DOC 举报

帧同步搜索电路是一种专门用于并行数据传输中的关键部件,它确保数据帧的正确接收和处理。电路设计的核心在于实现帧同步的检测和管理,以保证数据通信的稳定性和准确性。

在总体设计中,电路采用了分频器与状态机的组合架构,如图1所示。分频器被设定为10分频,其周期与帧长度相等,状态机则控制en和清零端口,当满足特定条件(如检测到所需次数的帧头)时,状态机会发出控制信号,使分频器进入正常工作模式,输出帧同步信号。

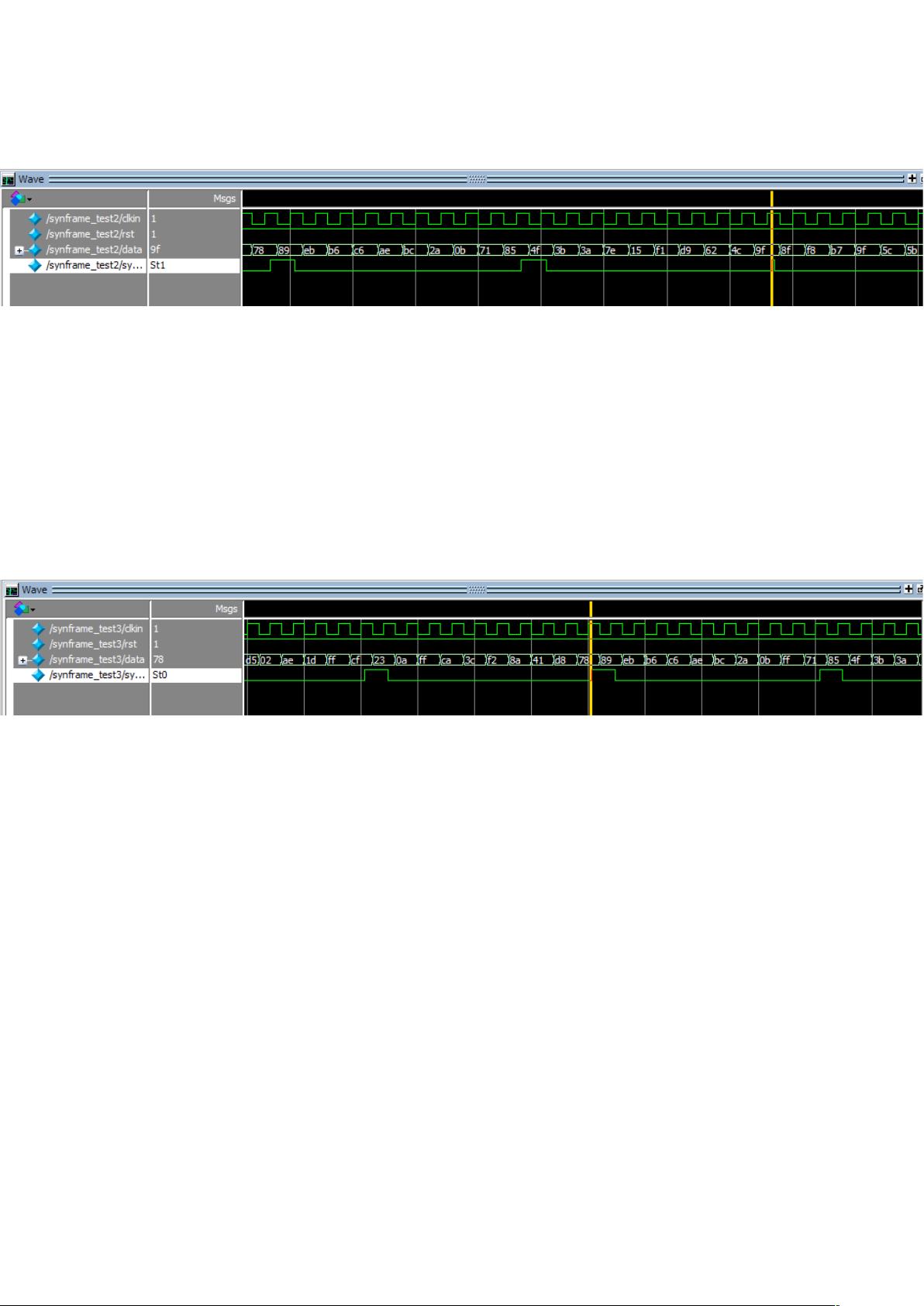

状态机是电路的灵魂,它定义了四个主要状态:IDLE(空闲)、SEARCH(搜索)、LOCK(锁定)和WARN(警告)。IDLE状态下系统初始化,未检测到帧头;SEARCH状态用于检测帧头,当连续三次检测到帧头后,计数器达到3,系统进入LOCK状态,表明帧同步建立;WARN状态表示出现错误的帧同步字,但仍处于可接受误差范围内。

电路的帧同步过程分为三个阶段:进入同步、保持同步和过滤假同步。当首次检测到帧头,SEARCH计数器启动,连续三次正确的帧头检测会导致同步锁定,输出稳定的同步信号,但可能存在一定延时。失去同步则是连续三次未检测到帧头,同步标志位停止输出。为了滤除数据流中的假同步,电路能够抵抗一定程度的干扰,即使遇到错误的同步字也不会误判。

然而,本次设计存在一些不足。首先,虽然进行了综合后的门级仿真,但完整的后仿真包括考虑门延时和布线延时,这是现代电路设计的重要环节,而后者在实际延迟中占据了很大比例。其次,设计过程中对不同风格描述的电路对门级仿真效果的理解不足,需要更深入地研究电路风格对仿真结果的影响。最后,电路对数据速率有一定的敏感性,当速率超过50MHz时,门级仿真可能会出现问题。

通过本次作业,学生深化了Verilog语言的应用,并实现了帧同步搜索电路的设计,但实践中仍需加强理论与实践的结合,优化电路设计,提高其鲁棒性和效率。

263 浏览量

102 浏览量

898 浏览量

207 浏览量

898 浏览量

2024-11-21 上传

111 浏览量

2023-06-20 上传

2021-07-13 上传

edgar1989

- 粉丝: 2

- 资源: 2

最新资源

- ehcache-2.8.0.zip

- 易语言学习-视频播放支持库(测试版) (1.0#0版).zip

- UI设计框架工具集 Semantic UI Kit .xd素材下载

- 行业分类-设备装置-烟熏炉的快拆式燃烧仓结构.zip

- device_oneplus_enchilada:OnePlus 6的设备树

- django-unicorn:神奇的Django全栈框架。 :sparkles:

- android nfc 读写demo

- shooter:使用node.js和HTML5制作的多人射击游戏

- 暑假儿童乐园PPT模板下载

- canal1.1.4(1.1.5).rar

- HackerRank-Problem-Solving:该存储库提供了用于解决hackerrank类别问题的解决方案。 解决方案是我创造的

- 易语言学习-超级加解密支持库 (1.1#0版)静态库版.zip

- 学习资料:超实用的双通道数据传输仿真和单片机源码(基于adc0832)-电路方案

- 免费年会抽奖软件特别版.rar

- linux平台远程桌面-基于Java AWT、SpringBoot、websocket、canvas的跨平台远程桌面实现

- storm_r1.1-adarna.zip