杭电数电实验:QuartusII逻辑设计与FPGA实现

版权申诉

"这是一份关于杭州电子科技大学数字电子技术实验课程的资料,包含了多个实验题目的设计答案。这些实验涉及到数字逻辑电路、Quartus II软件的使用、FPGA编程以及逻辑函数的实现。"

实验设计主要围绕以下几个知识点展开:

1. 数字逻辑电路:实验内容基于数字逻辑基础,涵盖了基本的逻辑门(如与非门)和更复杂的数字集成电路,如74138宏功能模块和7485二进制数值比较器。通过这些实验,学生能够理解和应用基本的数字逻辑概念。

2. Quartus II软件:作为Altera公司的 FPGA 设计工具,Quartus II 提供了原理图输入、HDL(硬件描述语言)输入以及混合设计方法。在实验中,学生需要学会如何使用Quartus II 创建工程、绘制电路图、进行编译、仿真和硬件测试。

3. 逻辑函数实现:实验题目要求学生使用Quartus II 中的74138宏功能模块来实现指定的逻辑函数。74138是一个八选一数据选择器,能够实现多路数据的切换,是数字系统设计中的常用组件。

4. 8位比较器设计:通过两片4位比较器7485的组合,学生将学习如何扩展逻辑电路以实现更复杂的功能,即构建8位比较器。这涉及到了逻辑电路的级联和扩展知识。

5. 8位串行进位加法器:实验中,学生首先需要设计一个全加器,然后利用8个这样的全加器构建8位串行进位加法器。全加器是加法运算的基础单元,而串行进位加法器则是多位加法器的一种实现方式。实验还包括时序仿真和硬件测试,以验证其正确性,并讨论其工作速度。

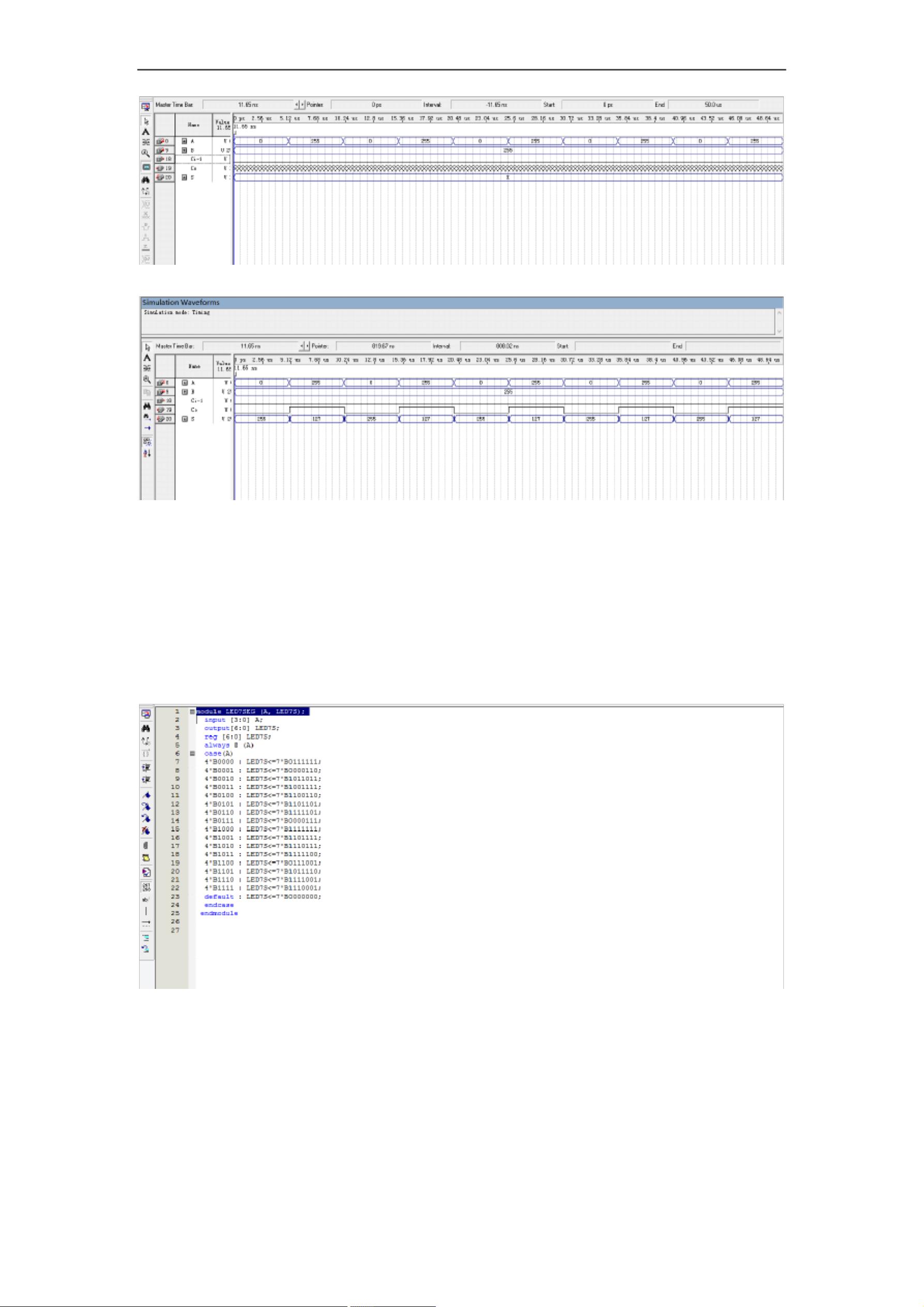

6. 7段显示译码器:实验中,学生需要用Verilog HDL编写代码实现一个7段显示译码器,特别是针对共阴极7段数码管的显示控制。这需要掌握Verilog的case语句以及译码器的工作原理。

每个实验不仅要求设计和实现电路,还要求进行时序仿真,以观察和分析电路的动态行为,确保设计的正确性。此外,实验还包括引脚锁定、编程下载至FPGA进行硬件验证,这是数字系统设计中的关键步骤,确保了设计在实际硬件上的可行性。最后,完成实验报告是对所学知识的总结和反思,有助于巩固理论知识与实践技能的结合。

4265 浏览量

点击了解资源详情

点击了解资源详情

313 浏览量

203 浏览量

2021-09-26 上传

xxpr_ybgg

- 粉丝: 6827

最新资源

- 罗克韦尔连接系统产品目录详览

- Swift高效刷题技巧分享,LeetCode实践心得

- 自动生成专业README的Node.js工具

- 掌握计划数据检查的要点与技巧

- Zipkin Jar包在微服务中的分布式追踪应用

- Struts2开发必备jar包及其Spring、JSON支持包指南

- 探索奥林板式换热器选型计算软件V15S的优势与特点

- SVN Patch自动化工具:快速提取版本改动文件

- 罗克韦尔CENTERLINE 2500马达控制中心手册

- Apache POI 3.8版本jar包详细介绍

- OpenShift快速部署模板:一键生成构建管道

- Reactjs结合socket.io打造聊天框前端

- OAuth 2.0 授权服务器示例详解

- yalmip工具包:Matlab平台的综合规划求解工具

- 《打开算法之门》:计算机算法的全面解析

- 海茵兰茨11-50SN编码器参数及安装指南