掌握序列检测器与FPGA设计:原理与实验实现

需积分: 0 107 浏览量

更新于2024-08-05

收藏 424KB PDF 举报

PB16060240实验是关于FPGA开发中的一个实践项目,主要聚焦于信号发生器、状态机和序列检测器的设计与实现。实验目标包括熟悉并掌握这些关键组件的工作原理,以及如何使用VHDL语言进行设计和实例化。以下是详细的实验内容概述:

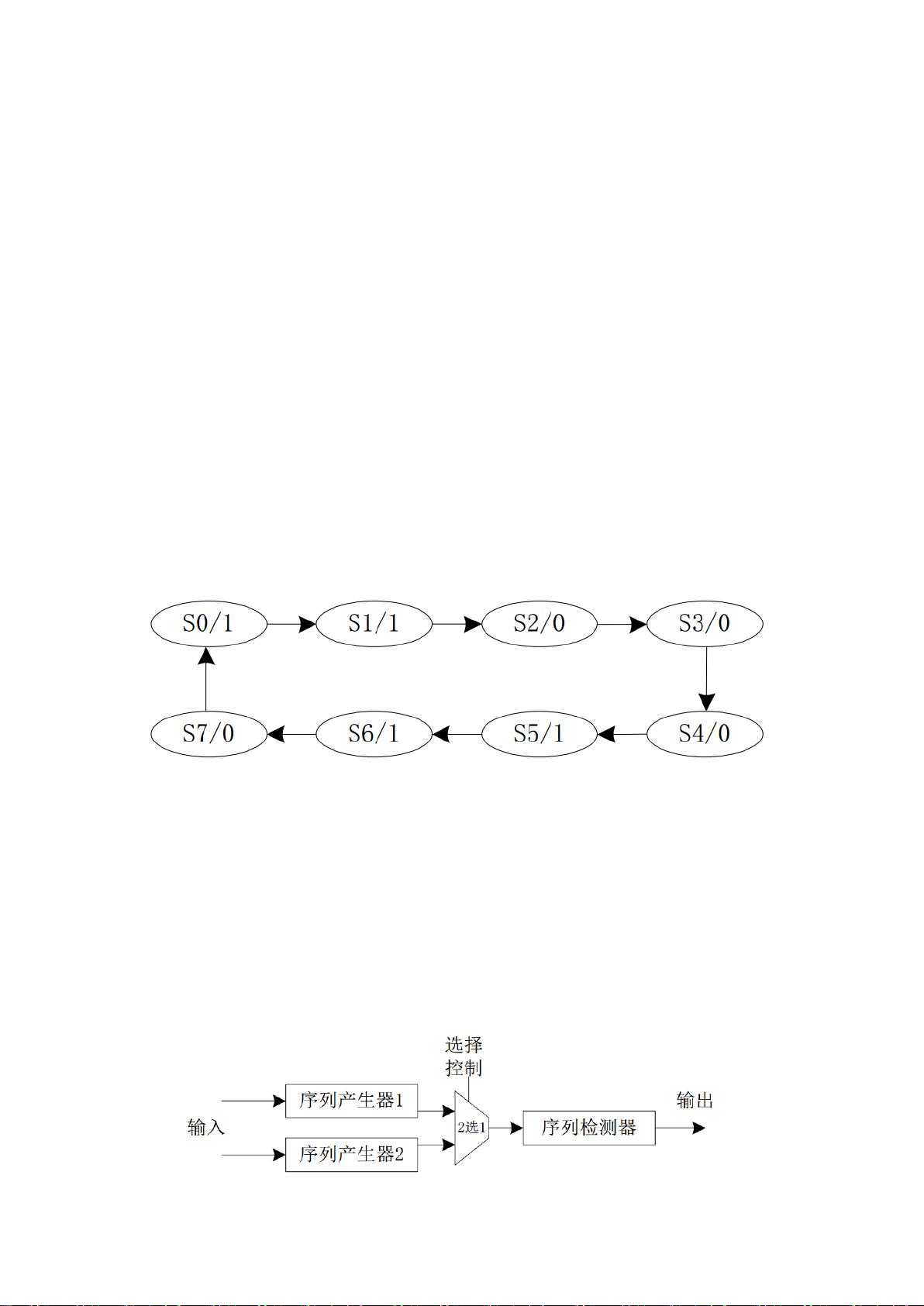

1. 信号发生器与状态机:实验者需要理解一个基于时钟的序列产生器的运作机制,即它是一个由时钟信号驱动的状态转换机,每个时钟周期会从一个状态转换到下一个,将状态映射成串行输出。这涉及到状态机的基本原理,如状态转移表或状态图的设计。

2. 序列检测器:不同于序列产生器,序列检测器负责接收外部的串行信号,并在内部进行匹配。实验设计中,没有采用状态转换机进行序列匹配,而是利用了另一种匹配算法,可能是简单的比较逻辑或者自适应算法。

3. 电路设计与仿真:实验包括设计完整的电路架构,如分频器用于稳定输出频率以便观察LED灯变化,以及序列发生器和数据选择器的选择功能。电路图展示了各个模块的连接和工作流程。此外,序列检测器利用串行信号队列进行匹配,当检测到预期的序列时,输出高电平信号。

4. VHDL编程:实验涉及到VHDL语言的使用,包括divider.vhd模块的设计,这是一个分频器,接受时钟信号并输出分频后的时钟。这个部分展示了VHDL的基本结构和语法规则,如端口声明、变量定义以及行为级或结构级设计。

5. 仿真结果与验证:顶层实体封装了输入(clk, sc, reset)和输出(output),当检测到匹配的序列时,输出为高电平。实验者需要通过仿真工具验证设计的正确性,确保序列检测器能准确识别输入序列。

总结来说,PB16060240实验是一个实战型的FPGA项目,旨在提升学生的硬件描述语言技能,理解并实现基本的数字逻辑电路,特别是序列生成和检测的硬件实现。通过这个项目,学生将深化对VHDL的理解,增强实际应用能力,并培养解决问题的系统级思考。

192 浏览量

点击了解资源详情

点击了解资源详情

2022-08-04 上传

107 浏览量

126 浏览量

2022-09-23 上传

2021-04-29 上传

139 浏览量

Xhinking

- 粉丝: 29

- 资源: 320

最新资源

- trading-using-options-sentiment-indicators

- CIS基础知识

- torch_cluster-1.5.6-cp37-cp37m-linux_x86_64whl.zip

- NOTHING ON THE INTERNET-crx插件

- 解决sqlserver 2012 中ID 自动增长 1000的问题.zip

- 在游戏中解谜游戏

- 导航栏左右滑动焦点高亮菜单

- Omicron35:正在进行中的Panda3D游戏

- Audio-Classification:针对“重新思考音频分类的CNN模型”的Pytorch代码

- be-the-hero-app:在OmniStack 11.0周开发的前端项目

- awvs12_40234.zip

- torch_sparse-0.6.4-cp37-cp37m-win_amd64whl.zip

- 团队建设讲座PPT

- 导航菜单下拉滑动油漆刷墙

- wkhtmltopdf.zip

- ShapeShit:软件开发