《数字逻辑设计基础》第七章习题详解:触发器功能与波形设计

需积分: 13 41 浏览量

更新于2024-08-04

收藏 6.7MB DOCX 举报

本资源是一份关于《数字逻辑设计基础(第二版)》的第七章课后习题及答案文档,由何健新和曾祥萍两位主编编撰。该章节深入探讨了数字逻辑中的各种触发器及其功能,包括:

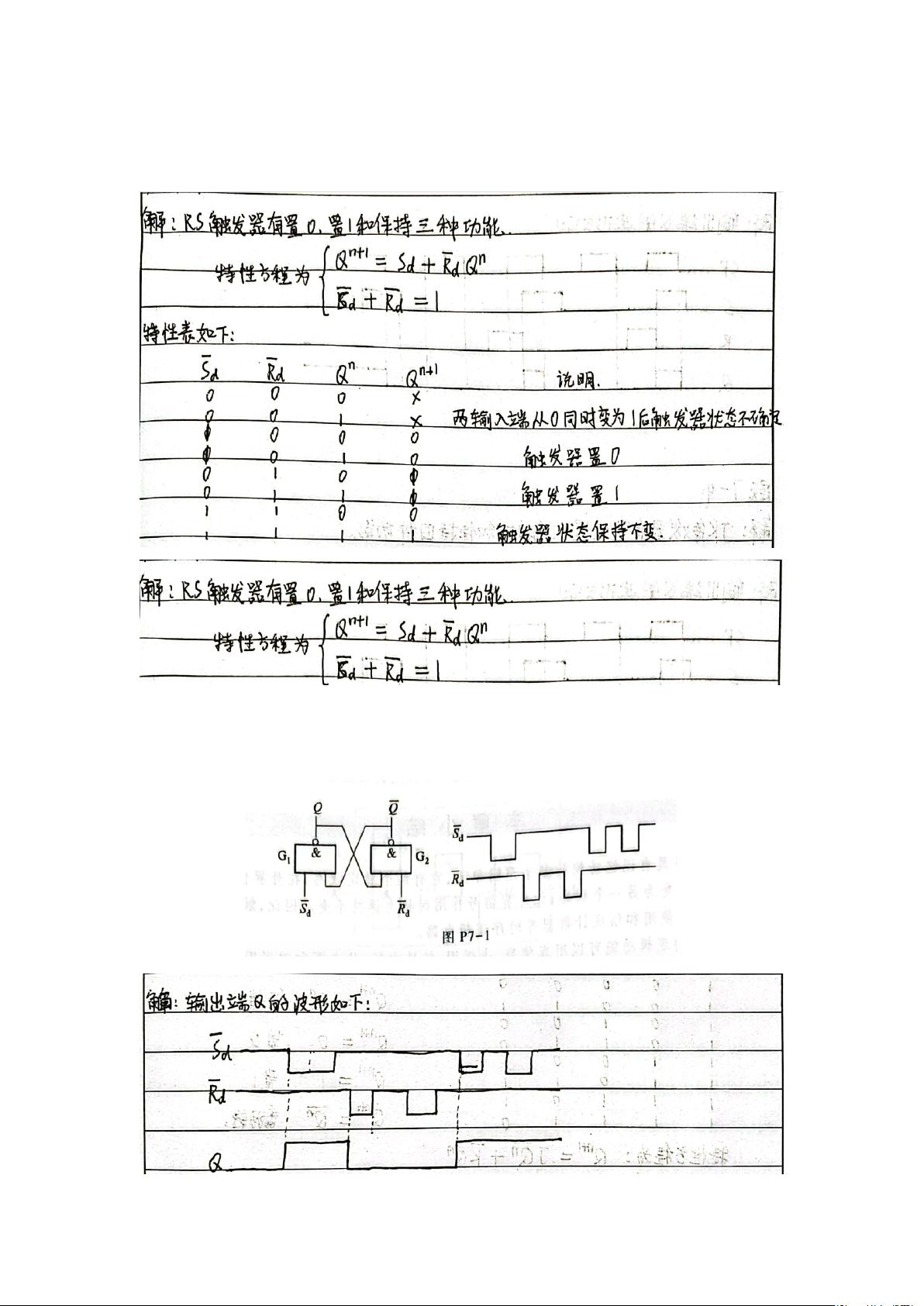

1. 尺5触发器:这种触发器的功能多种多样,其特征方程和特性表是学习者需要掌握的基础。尺5触发器的不同功能取决于其内部结构和配置,解题时需理解并推导其工作原理。

2. 基本RS触发器:题目要求画出Q的状态波形,这涉及到时序逻辑分析,需要根据输入S和R以及Q的初始状态来描绘输出Q随时间的变化。

3. 同步RS触发器:与RS触发器类似,但涉及同步时钟的影响,解题时需要考虑时钟周期内的逻辑行为。

4. JK触发器:这是一种通用型触发器,有多种功能,特征方程和特性表可以帮助学习者理解它的逻辑功能,包括置零、置1、保持和翻转等。

5. D触发器:D触发器基于D输入决定输出状态,同样需要编写特征方程和特性表,同时题目要求根据特定CP和D输入波形绘制Q的波形。

6. 高电平有效和上升沿有效的D触发器:这种触发器在CP上升沿发生时更新状态,解题时需结合CP和D波形来展示输出变化。

7. 维持-阻塞D触发器:此题要求画出输出Q的工作波形,通常这类触发器具有保持状态的能力,初始状态为0时,输出如何响应输入信号是关键。

8. JK触发器的异步置位和复位:根据输入信号J、K、CP、异步置位端S的波形,模拟触发器的行为并绘制Q的波形。

9. 上升沿触发的JK触发器:在这个问题中,初始状态为1,解题时需注意触发条件对输出Q的影响。

10. 图P7-7中的触发器波形分析:题目提供了一个电路和CP波形,需要根据初始状态0分析Q1和Q0的波形演变。

11. Verilog程序设计:下降沿触发的D触发器模块被设计为在CP下降沿时更新Q状态,测试代码展示了如何通过系统级仿真验证这个功能。

12. 下降沿触发D触发器的波形:根据输入波形,模拟输出Q的波形变化,初始状态为0的情况下,探讨触发器的行为。

13. 使用VHDL描述触发器:题目可能要求读者用VHDL语言描述一个触发器,这是硬件描述语言的实际应用,涉及电路设计和语法规则。

这些习题涵盖了数字逻辑的基本概念和实践技能,对于学习者来说,解答这些问题将有助于深化对数字逻辑触发器的理解,掌握它们的时序特性和行为。通过解决这些问题,学生可以提升设计和分析数字逻辑电路的能力。

点击了解资源详情

点击了解资源详情

134 浏览量

2021-09-19 上传

156 浏览量

2022-07-13 上传

2022-07-09 上传

2023-03-22 上传

2021-11-09 上传

qing影

- 粉丝: 1444

最新资源

- 安卓动画库Persei:Yalantis开源动画的Java实现

- 掌握整流电路原理及应用的免费学习教程

- 意法半导体STM32F2xx固件库使用详解

- IC卡数据读写工具 - M1卡扇区信息获取

- Luban压缩算法:图片优化的未来之星

- Maya动画练习:16个动物角色模型绑定指南

- C#代码挑战解决方案集锦

- Python工厂操作系统开发教程

- SSMA环境搭建指南:从安装到使用

- 蓝宙双电机编码器检测程序功能详解

- Opencart VQMOD扩展实现多文件上传功能

- 新Twitter界面的极简主义主题设计

- 掌握C语言实现经典密码算法教程

- Angular开发环境搭建与代码脚手架使用指南

- 如何将Excel文件转换为TXT格式

- 使用JavaScript实现coinflip翻硬币效果