Xilinx Spartan-6 FPGA DDR3开发指南详解

需积分: 34 100 浏览量

更新于2024-07-21

1

收藏 2.07MB PDF 举报

"Xilinx Spartan-6 FPGA DDR3开发手册"

Xilinx Spartan-6 FPGA DDR3开发手册是针对使用Xilinx Spartan-6系列FPGA进行DDR3内存接口设计的专业指南。该手册提供了详尽的指导,旨在帮助工程师们理解和实现高效的DDR3内存控制器,从而在系统设计中充分利用Spartan-6 FPGA的内存接口功能。

手册涵盖了多个关键知识点,包括:

1. **DDR3内存技术概述**:DDR3是一种高速、低功耗的动态随机存取存储器(DRAM)标准,其工作原理、速度等级、数据传输速率等特性在手册中得到了详细解释。

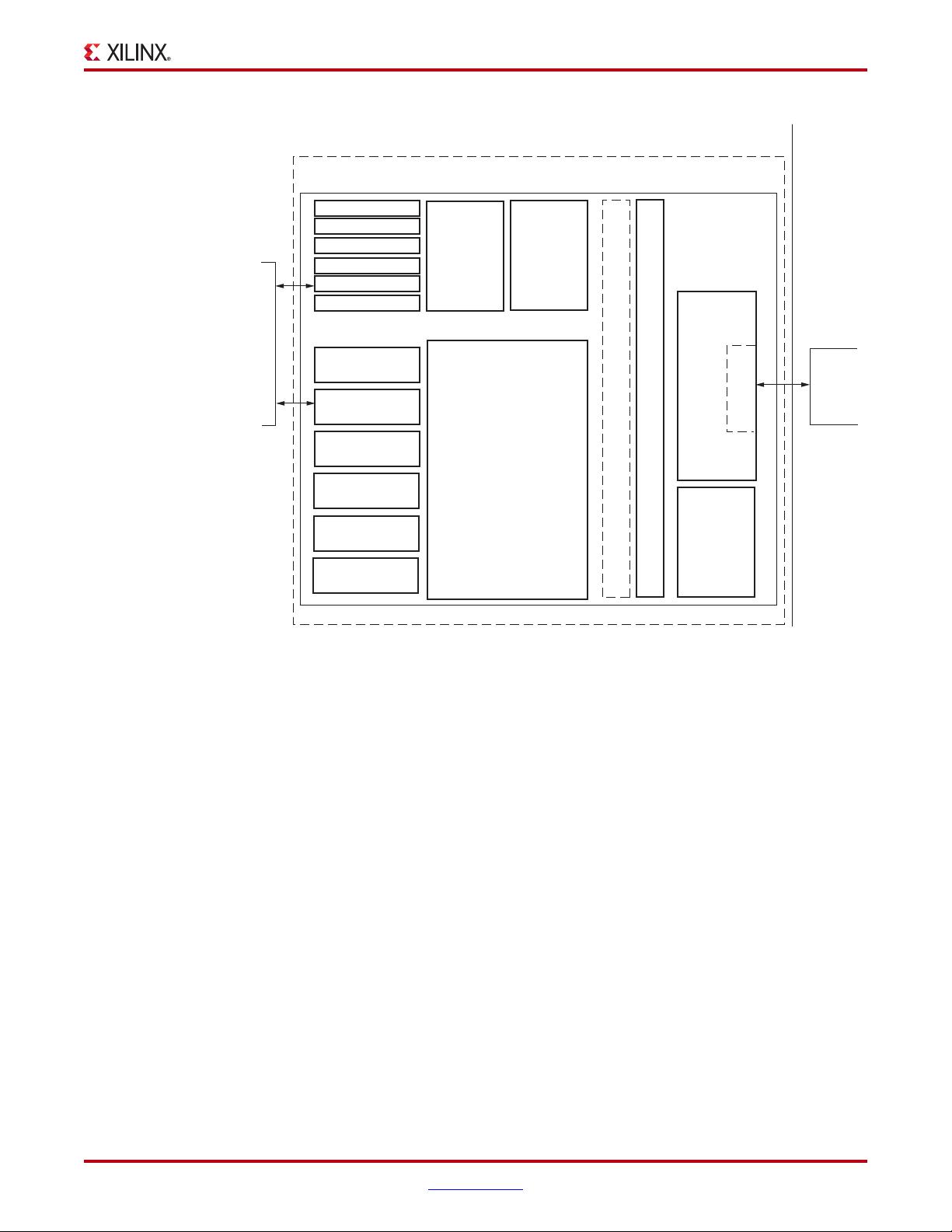

2. **Spartan-6 FPGA架构**:手册深入介绍了Spartan-6 FPGA的内存块(BRAM)、分布式内存和I/O资源,以及如何利用这些资源来构建DDR3内存控制器。

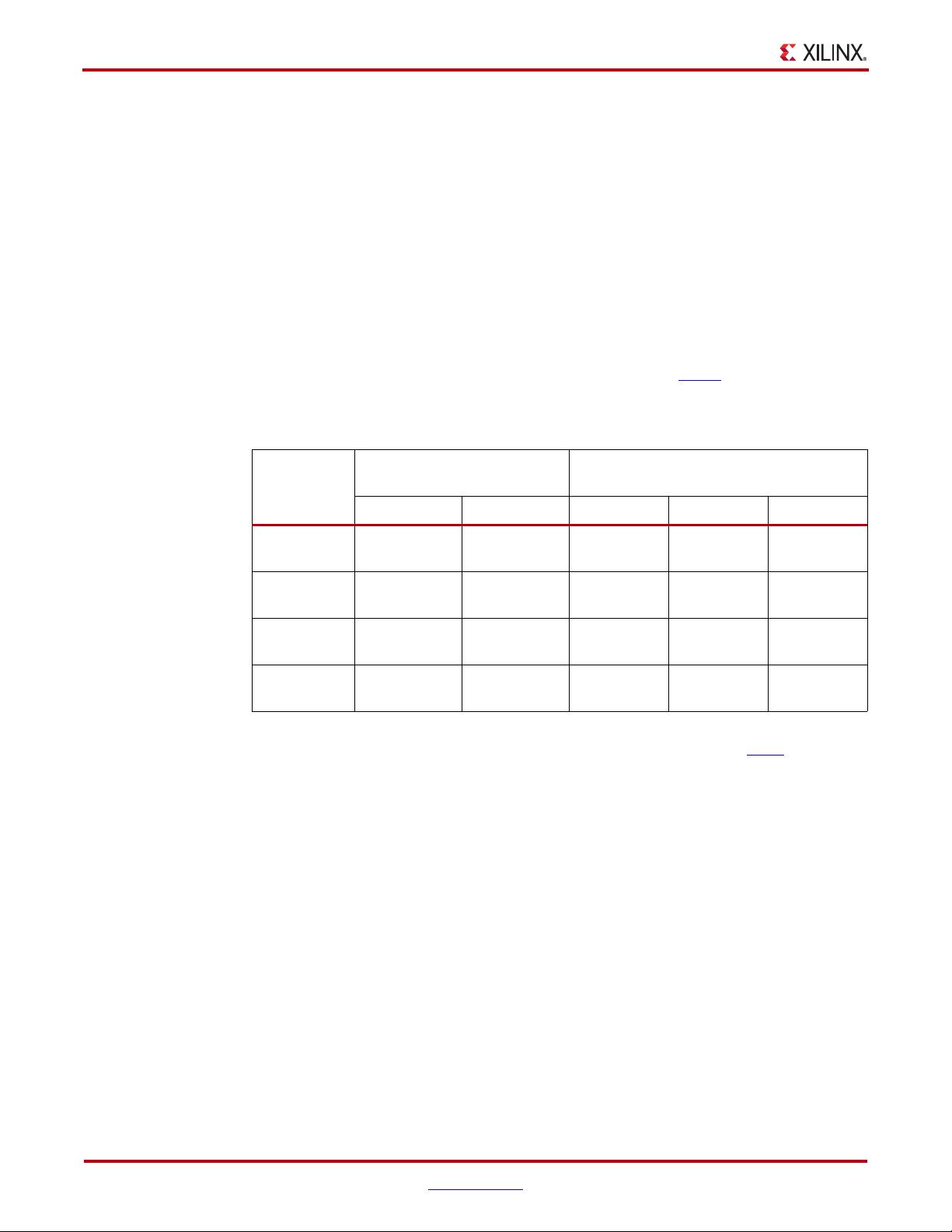

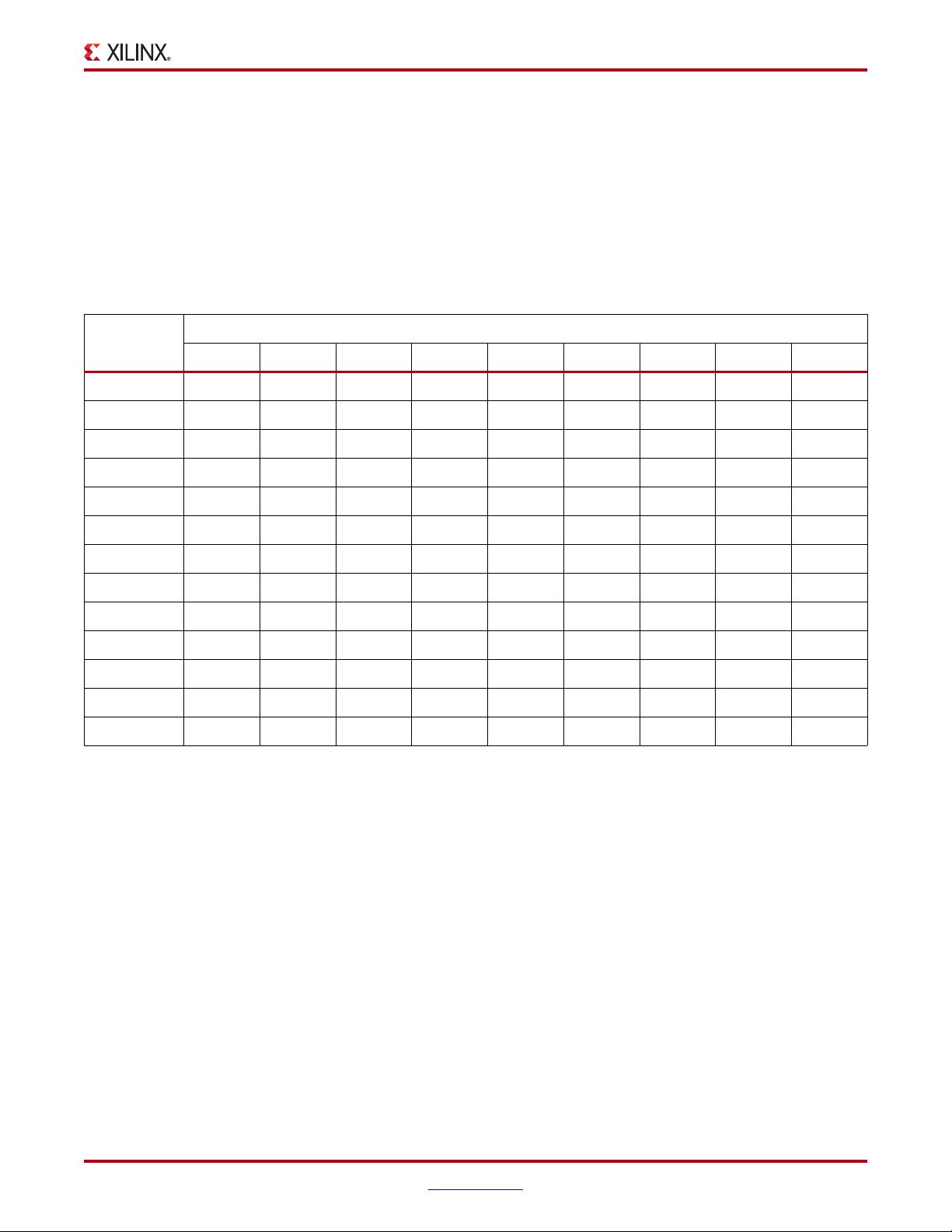

3. **内存控制器配置**:包括时序参数设置、预读取(Prefetching)、写入后读取(Write-Read-After-Write, WRAP)模式、突发长度(Burst Length)、列地址交错(Bank Interleaving)等,这些都是优化内存性能的重要因素。

4. **时钟管理**:DDR3内存操作对时钟同步有严格要求,手册会详细讲述如何使用Spartan-6 FPGA的全局时钟网络和时钟缓冲器(DLL, DCM)来满足这些要求。

5. **接口信号定义**:手册详细解析了DDR3接口的信号线,如地址线、数据线、控制线和时钟线,以及它们在FPGA和DDR3内存芯片间的交互方式。

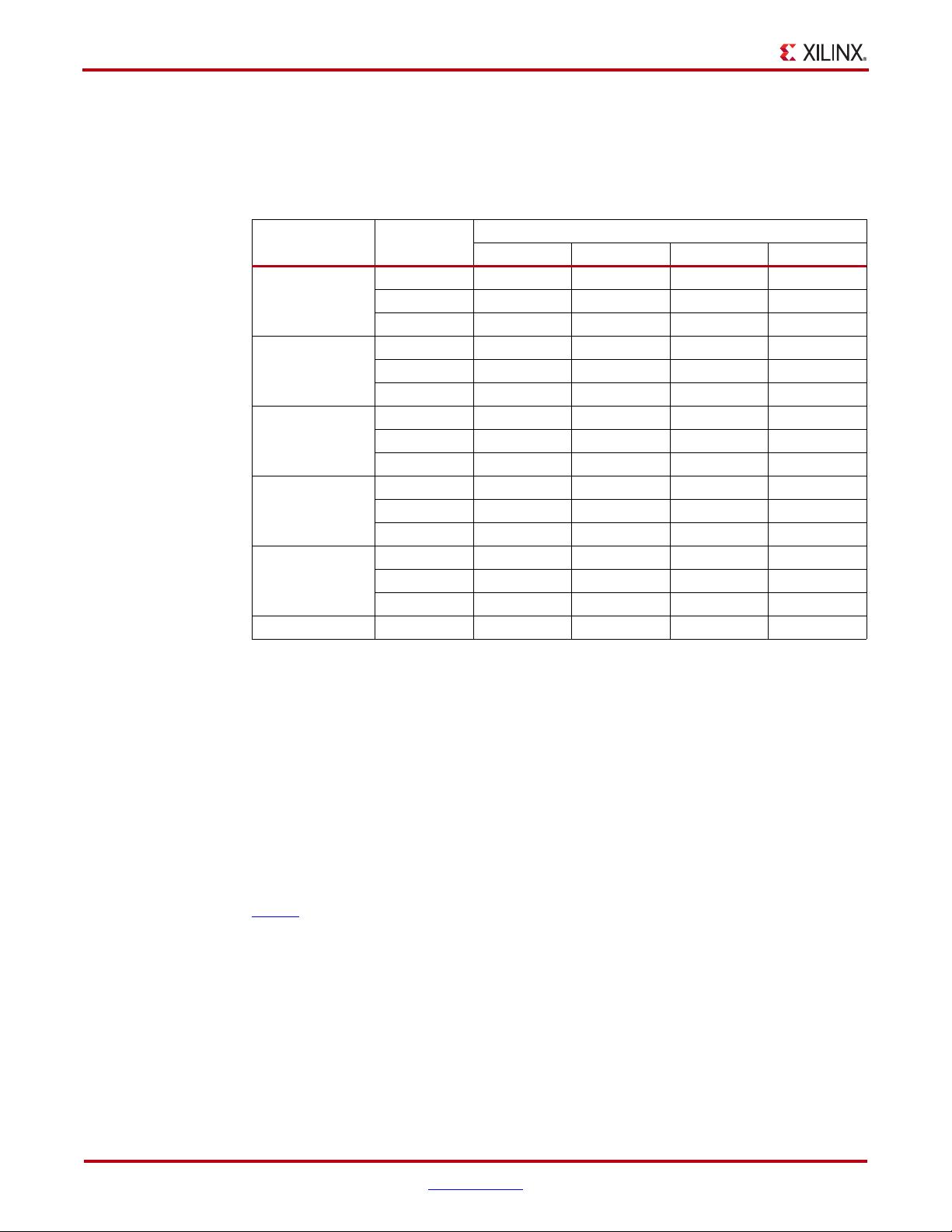

6. **设计流程**:从逻辑设计到硬件实现,手册提供了完整的DDR3内存控制器设计步骤,包括使用Xilinx的VHDL或Verilog HDL进行编码、时序约束设定、综合、布局布线以及仿真验证。

7. **IP核集成**:Xilinx提供预配置的DDR3控制器IP核,手册指导用户如何在Xilinx ISE或Vivado设计套件中集成和配置这些IP核。

8. **故障排查与调试**:手册还包含了一些常见问题及解决方法,帮助开发者诊断并修复设计中的错误。

9. **合规性与限制**:手册强调了Xilinx关于使用和分发文档的政策,包括版权和许可条款,以及使用文档进行设计的风险和责任。

10. **技术支持与更新**:尽管Xilinx不承担技术支持的义务,但手册可能会提示用户如何获取最新的更新和技术支持资源。

这份手册是开发基于Spartan-6 FPGA的DDR3内存系统时不可或缺的参考资料,它提供了从理论到实践的全面指导,帮助工程师克服设计挑战,实现高效可靠的内存接口。

473 浏览量

2379 浏览量

311 浏览量

139 浏览量

2019-08-24 上传

122 浏览量

169 浏览量

2022-09-24 上传

dengxf01

- 粉丝: 40

- 资源: 64