Verilog_HDL实现的FPGA乐曲演奏电路设计

"基于Verilog_HDL的乐曲演奏电路设计"

本文主要探讨了一种使用EDA技术,特别是基于Verilog HDL的乐曲演奏电路设计方法。随着电子设计自动化(EDA)技术的进步,使用可编程逻辑器件如FPGA来实现复杂的数字系统设计变得日益普及。在传统的数字逻辑设计中,实现乐曲演奏的硬件电路非常复杂,但借助于现代EDA工具和硬件描述语言,这一挑战可以得到有效的解决。

课程设计的核心是采用FPGA(Field-Programmable Gate Array)器件来驱动小扬声器播放音乐。选用的FPGA型号为Altera的EPF10K10,设计过程则在MAX+plusⅡ软件平台上进行。MAX+plusⅡ是一款由Altera公司提供的电子设计自动化工具,特别适用于CPLD和FPGA的设计与开发。

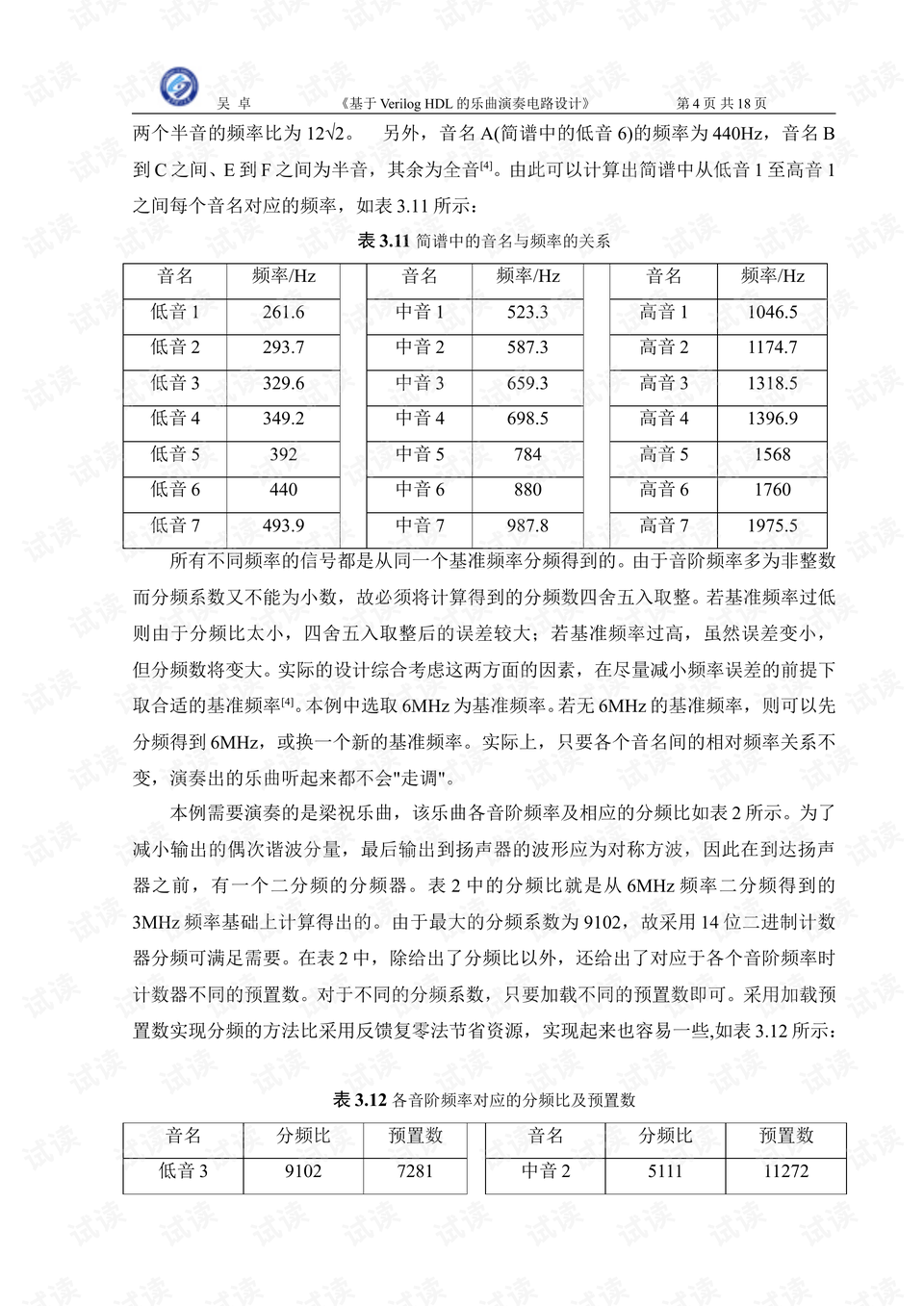

乐曲演奏电路的设计目标是通过Verilog HDL进行编程,以实现分频控制的方式,进而控制音调的高低变化和音长。Verilog HDL是一种硬件描述语言,它允许设计者以接近自然语言的方式描述数字系统的硬件行为和结构,从而实现电路的功能。在这个设计中,每个音调对应一个特定的频率,通过控制激励信号的频率和持续时间,能够使扬声器发出连续的音乐,并在乐曲结束时自动重头播放。

课程设计的具体要求包括:首先,能够精确控制激励信号的频率以产生不同音调;其次,确保声音的持续时间正确,以保持音乐的节奏和旋律;最后,实现乐曲的自动循环播放,即在一首乐曲结束后,系统能自动返回到乐曲的开头继续演奏。

EDA技术是电子设计的关键工具,它整合了电子技术、计算机技术和信息处理等多个领域的最新成就,为电子产品的设计提供了自动化平台。EDA工具如VHDL(Very High Speed Integrated Circuit Hardware Description Language)和Verilog HDL,允许设计者用文本或图形方式描述硬件行为,简化了复杂电子系统的设计流程。

在本文中,通过一个具体的乐曲演奏电路设计案例,读者可以了解到如何运用EDA工具,特别是Verilog HDL,来实现一个基于FPGA的音乐播放系统。这样的设计不仅加深了对EDA技术的理解,同时也展示了硬件描述语言在实现音乐播放等复杂功能中的实用性和灵活性。

相关推荐

hunningtu_lq

- 粉丝: 2

最新资源

- ALonelyPlace: 探索太空与海洋的诗歌艺术之旅

- 分析Python urllib2模块HTTP基本认证Bug与HTTPError处理

- 宠物管理系统:适合学习的简单JavaWeb程序

- 深入理解C++/C编程技巧与最佳实践

- C++实现的蜘蛛纸牌游戏详解

- WIN32API实现的高效关机小程序功能介绍

- 高效背单词小程序:记录与巩固生词神器

- 精选3款404错误页面模板免费下载

- C语言实现LDPC编码解码技术详解

- 图解GSM第三层信令及基础知识

- 深入理解缓存技术及其应用

- ASP网上书店数据库设计与后台管理

- ML-KNN-Bayes:基于Scikit-Learn的分类器构建与比较

- 微信界面与元素的高清图片集锦

- Android引导动画实现与sharepreferences应用教程

- 遗传算法在动力配煤中的GUI界面实现及MATLAB调试