NCOIPcore在Chirp函数设计中的应用

164 浏览量

更新于2024-08-31

收藏 240KB PDF 举报

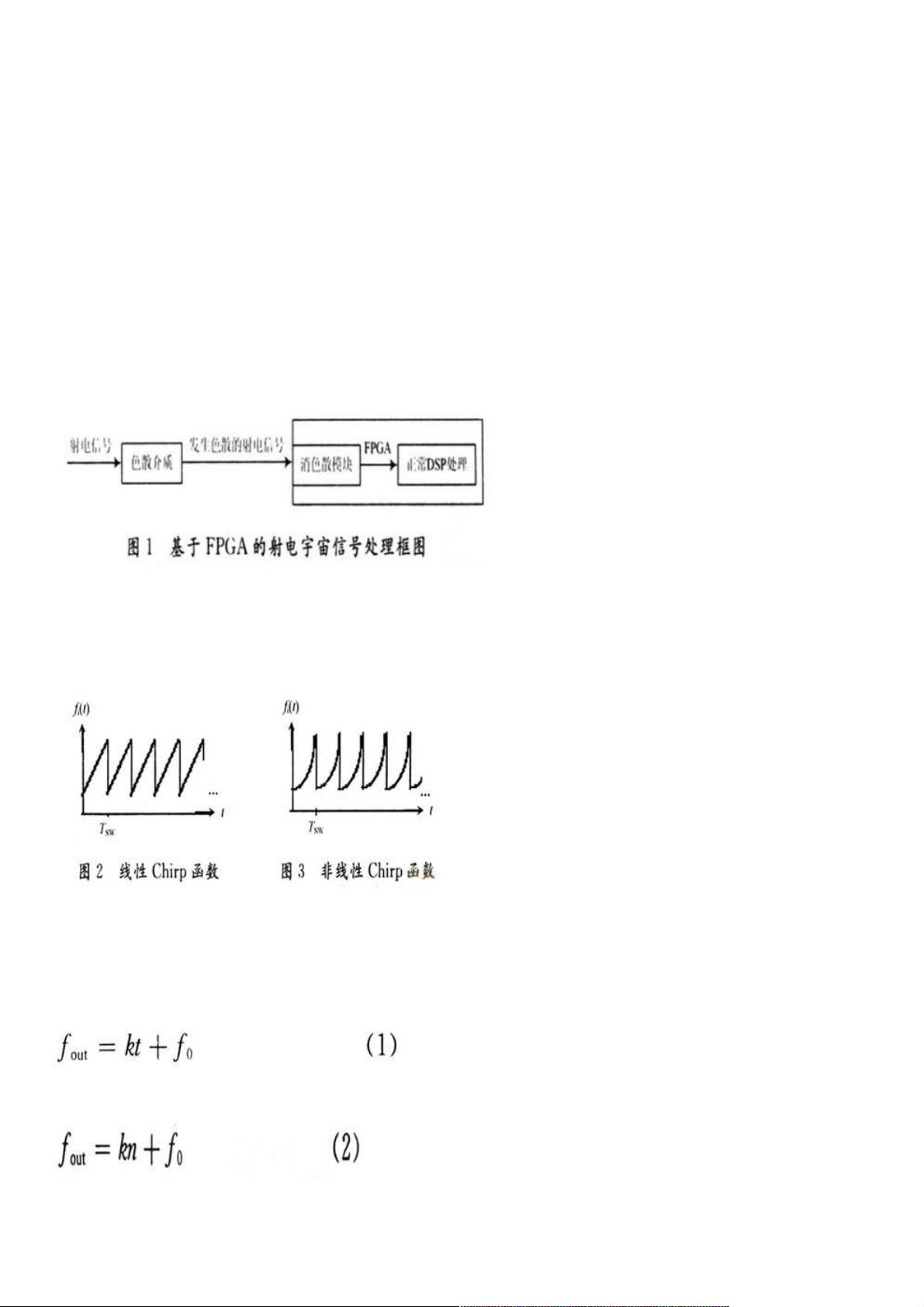

"本文主要探讨了基于NCOIPcore实现Chirp函数的设计方法,阐述了IP核在电子设计中的重要性,特别是在FPGA和CPLD应用中的优势。文中提到了几种常见的IP核,如FIR滤波器、FFT核心和NCO核心,并指出使用这些预设计的IP核能有效简化设计流程,提高设计效率和性能。Chirp函数,即扫频信号,是通过改变NCOIPcore的输入频率控制字来实现的,分为线性和非线性两种类型。文章详细介绍了线性和非线性Chirp函数在频域和时域的关系式,为实际应用提供了理论基础。"

在现代电子系统设计中,IP核(知识产权核)扮演着至关重要的角色。它们是预先设计并验证过的电路模块,可以被集成到ASIC或FPGA/CPLD中,以加速开发进程,提高设计质量。IP核分为软IP(逻辑描述)、固IP(门级网表)和硬IP(物理布局),分别对应不同的设计阶段和应用需求。

NCO(数控振荡器)IP核是其中的一种关键组件,它能够生成精确的数字频率输出。在本设计中,NCOIPcore被用来实现Chirp函数,这是一种频率随时间线性或非线性变化的信号。Chirp函数在雷达、通信和信号处理等领域有着广泛的应用,例如在雷达系统中用于目标的检测和距离测量。

线性Chirp函数的频率随时间线性增加,其数学表达式在连续和离散时间域中有所不同。非线性Chirp函数则更为复杂,其频率随时间的变化遵循一个非线性函数。在设计中,通过实时调整NCO的输入频率控制字,可以灵活地生成所需类型的Chirp信号。

使用NCOIPcore实现Chirp函数的优势在于能够精确控制频率变化,同时减少了设计者在底层算法和硬件实现上的工作负担。此外,由于IP核通常经过优化,其运算精度、速度以及信噪比(SNR)和失真度(SFDR)等关键性能指标通常优于自定义设计,从而确保了系统的高效运行和高质量输出。

基于NCOIPcore的Chirp函数实现是一种高效、灵活的设计策略,它结合了IP核的优势和Chirp函数的独特性质,为电子系统设计提供了强大的工具,尤其是在需要动态频率调制的场景下。通过深入理解和应用这些技术,设计者能够更好地满足日益复杂的电子系统需求。

2023-05-15 上传

2024-09-12 上传

2023-06-21 上传

2023-06-01 上传

2024-01-21 上传

2023-06-28 上传

2023-05-13 上传

2023-08-08 上传

weixin_38717843

- 粉丝: 1

- 资源: 923

最新资源

- WebLogic集群配置与管理实战指南

- AIX5.3上安装Weblogic 9.2详细步骤

- 面向对象编程模拟试题详解与解析

- Flex+FMS2.0中文教程:开发流媒体应用的实践指南

- PID调节深入解析:从入门到精通

- 数字水印技术:保护版权的新防线

- 8位数码管显示24小时制数字电子钟程序设计

- Mhdd免费版详细使用教程:硬盘检测与坏道屏蔽

- 操作系统期末复习指南:进程、线程与系统调用详解

- Cognos8性能优化指南:软件参数与报表设计调优

- Cognos8开发入门:从Transformer到ReportStudio

- Cisco 6509交换机配置全面指南

- C#入门:XML基础教程与实例解析

- Matlab振动分析详解:从单自由度到6自由度模型

- Eclipse JDT中的ASTParser详解与核心类介绍

- Java程序员必备资源网站大全