Verilog 实现FPGA全并行与半并行乘法器

需积分: 50 149 浏览量

更新于2024-09-13

1

收藏 299KB DOCX 举报

“FPGA 乘法器的设计与实现,包括全并行乘法器和流水线乘法器的Verilog HDL代码示例,以及逻辑实现与使用DSP48资源的对比。”

在数字系统设计中,乘法运算是一种基本操作,尤其是在FPGA(现场可编程门阵列)应用中,例如在常系数FIR滤波器中。在FPGA中,乘法器可以有两种主要实现方式:逻辑实现和利用硬核资源,如Xilinx FPGA中的DSP48单元。逻辑实现虽然灵活,但可能占用更多的逻辑资源,而使用DSP48则能提供更快的计算速度,但数量有限。

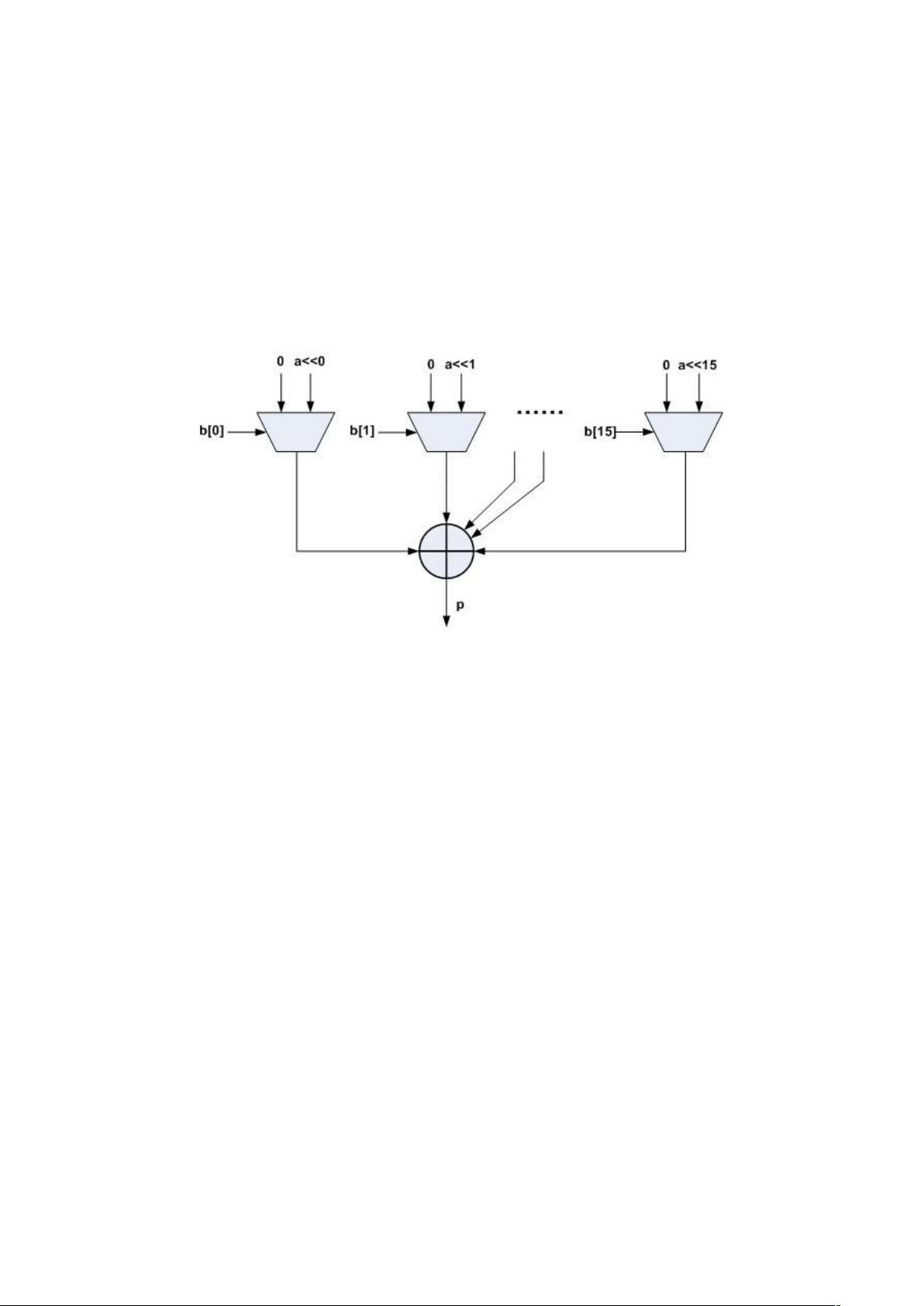

全并行乘法器是一种高效的逻辑实现方法。正如描述中提到的,全并行结构乘法器可以在一个时钟周期内完成16位无符号数的乘法,输出延迟仅一个时钟周期。其工作原理是将两个输入数据a和b并行输入,然后通过多次移位和累加来得到结果。图1展示了这种结构,但在这里无法显示具体图形。

在Verilog HDL中,全并行乘法器的实现可以参考给出的代码段。代码中定义了一个名为`multiply_lut_FP`的模块,它接受两个16位输入`a`和`b`,以及一个时钟信号`clk`和复位信号`rst`。通过生成语句(`generate`)和`for`循环,实现了每个位的乘法,并将结果累加到总和变量`p`中。该实现使用了64个Slice Registers和598个Slice LUTs,这表明它相对资源密集,但在速度上提供了优势。

此外,流水线乘法器是另一种优化设计,它通过将乘法过程分解为多个阶段来提高吞吐量,每个阶段在一个时钟周期内完成一部分计算。流水线结构允许在不同时钟周期处理新的输入,从而在保持高效率的同时提高了系统整体的处理能力。流水线乘法器通常适用于需要连续处理大量数据的场合。

在设计FPGA乘法器时,设计师需要权衡速度、资源利用率和功耗等因素。对于资源紧张但速度要求高的应用,全并行结构可能更合适;而在资源充足,且对实时性要求不那么严格的情况下,流水线结构可以提供更好的资源利用率。因此,理解不同乘法器结构的特点和适用场景,是优化FPGA设计的关键。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-07-15 上传

2022-09-14 上传

2013-04-23 上传

2015-03-21 上传

2014-03-23 上传

lz_15219600

- 粉丝: 1

- 资源: 3

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析