Nios II处理器外围设备详解:从PIO到DMA

需积分: 9 178 浏览量

更新于2024-07-22

收藏 2.65MB PPT 举报

"本章详细介绍了Nios II处理器的常用外围设备,包括它们的硬件结构、核心特性、SOPCBuilder中的配置选项以及软件编程方法。这些外围设备以IP核的形式提供,用户可以根据需求将它们集成到自定义的Nios II系统中。章节涵盖了并行输入/输出(PIO)内核、SDRAM控制器、CFI(通用Flash)控制器、EPCS控制器、定时器、UART、JTAG_UART、SPI、DMA、带Avalon接口的互斥内核、邮箱内核和SystemID内核等多个重要组件。"

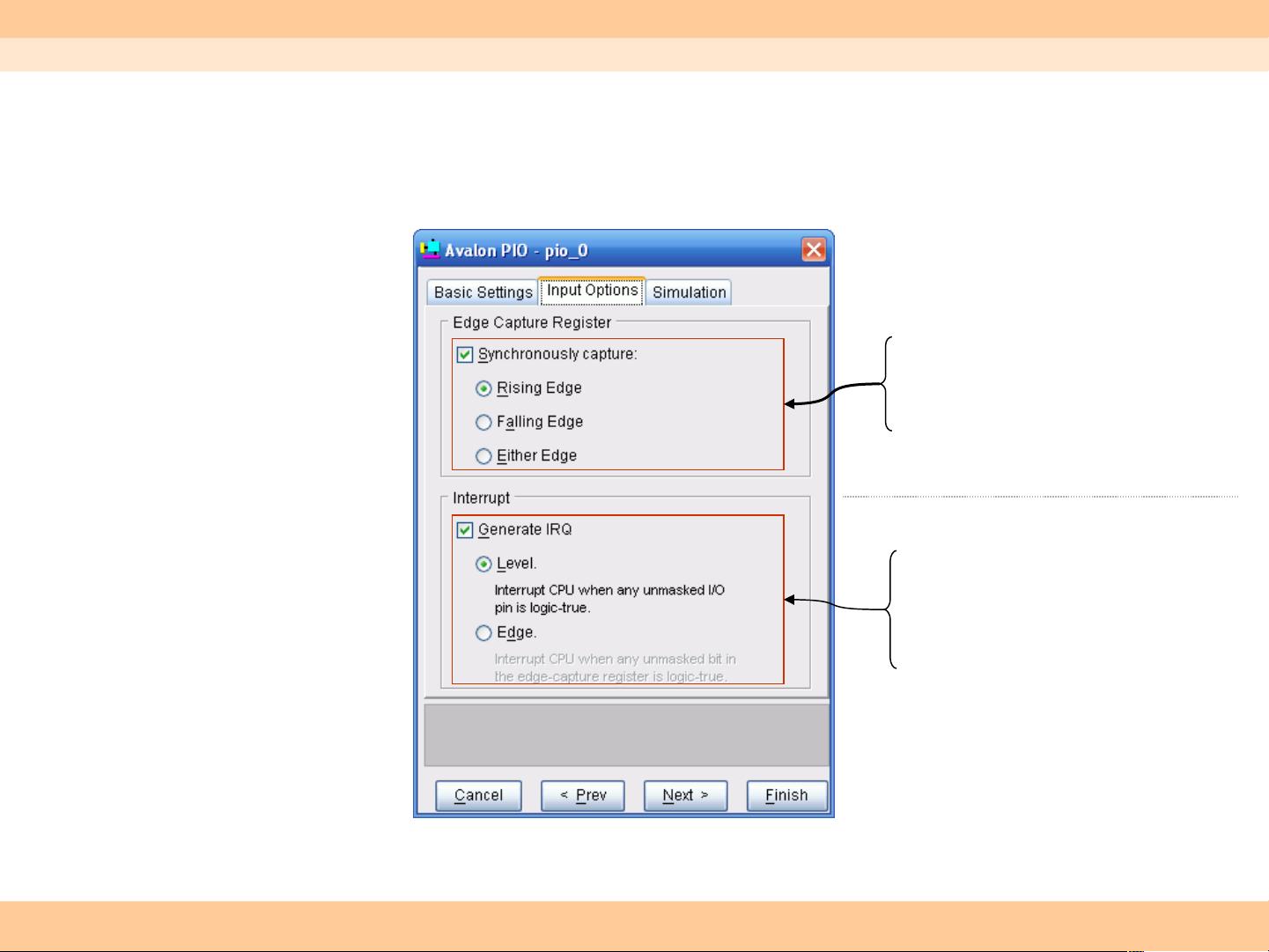

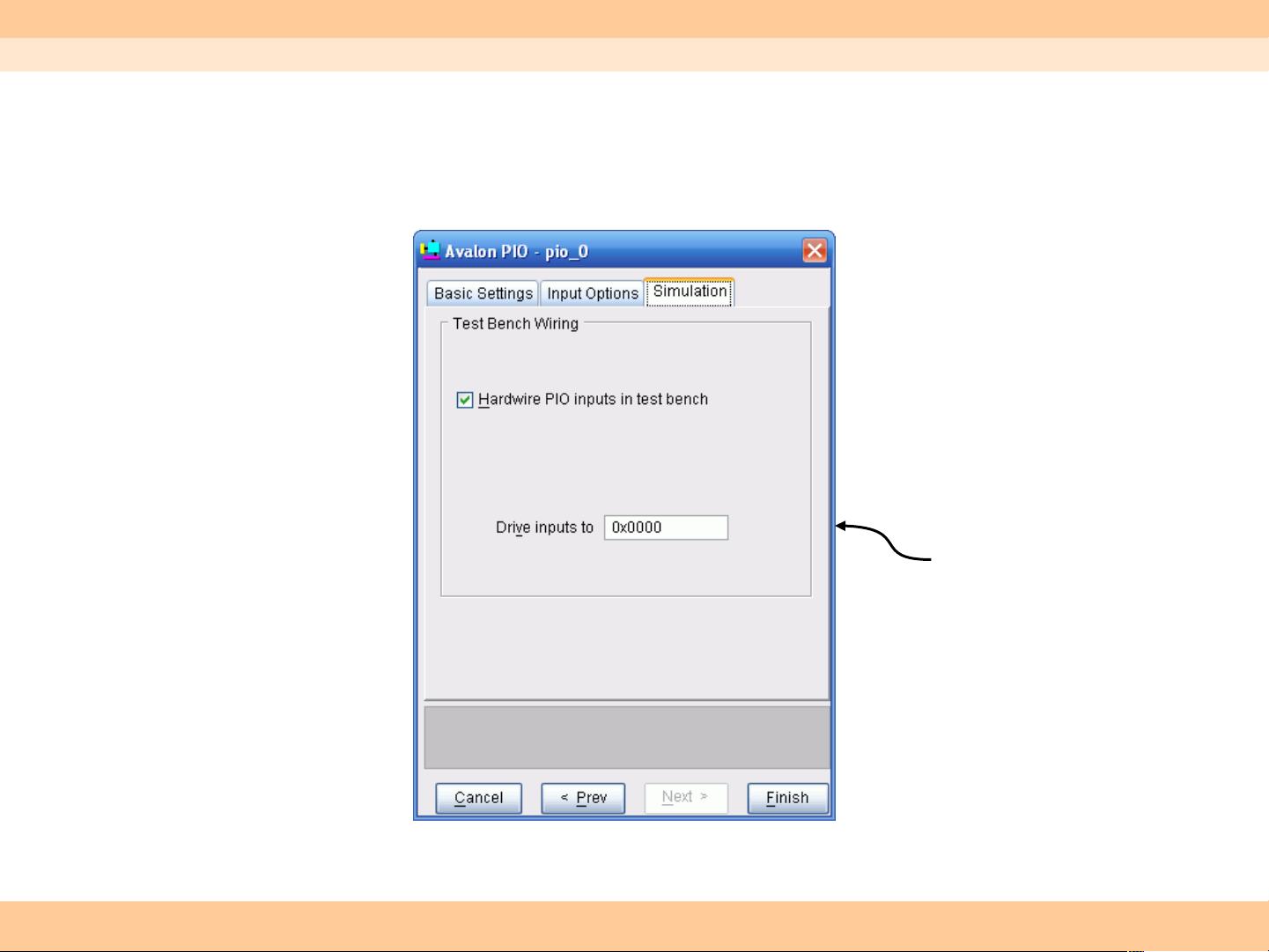

在Nios II处理器的外围设备中,首先提到的是并行输入/输出(PIO)内核,它作为一个Avalon从控制器,提供了与通用I/O口之间的内存映射接口,用于简单I/O访问,如控制LED、读取开关、驱动显示设备或与外部设备通信。在SOPCBuilder中,用户可以方便地集成PIO内核,并且该内核支持最多32个I/O端口,其端口数量是可配置的。

接下来,章节讨论了SDRAM控制器内核,它负责管理Nios II系统对SDRAM的访问,确保数据传输的正确性和效率。此内核的配置选项包括SDRAM的大小、时序参数等,对于高速、大容量的数据处理至关重要。

CFI(通用Flash)控制器内核则用于管理与非易失性存储器的交互,如Flash存储器,通常用于存储程序代码和系统数据。EPCS控制器则专用于配置基于EPCS协议的外部存储器,如配置存储器或FPGA的初始化数据。

定时器内核是嵌入式系统中常见的组件,用于计时、中断触发以及其他时间相关的任务。UART(通用异步收发传输器)内核提供了串行通信能力,常用于与串口设备通信,而JTAG_UART内核则结合了UART功能和JTAG调试接口,便于系统调试。

SPI(串行外围接口)内核则提供了与SPI兼容的设备进行通信的能力,广泛应用于传感器、显示模块等。DMA(直接内存访问)内核允许数据在内存和外设之间高速传输,减轻CPU负担。

带Avalon接口的互斥内核和邮箱内核是实现系统内不同组件间同步和通信的关键,前者用于资源的独占访问,后者作为消息传递的机制。最后,SystemID内核提供了系统识别信息,有助于系统识别和版本管理。

这些外围设备的详细介绍和配置,加上相应的软件编程指南,构成了设计和优化Nios II系统的基础,使得开发者能够根据具体应用需求构建高效、功能丰富的嵌入式解决方案。

2020-11-27 上传

2011-05-06 上传

2021-06-10 上传

2021-09-21 上传

2013-12-12 上传

2015-10-04 上传

2009-09-25 上传

2010-12-21 上传

ssike123

- 粉丝: 0

- 资源: 1

最新资源

- zigbee2006协议规范完整版(中文)

- Study ARM Step by Step(中文版)

- C语言程序设计(经典教材)

- 一步一步基于ADS1.2进行设计开发

- 软件测试_浅谈软件测试流程

- 经纪人管理系统过程测试

- 《信息论与编码》第2版 陈运 课后习题答案

- Introducing Microsoft SQL Server 2008

- FPGA语言简易教程

- java面试题(张孝祥老师整理)

- linuxC.pdf

- The One Page Project Manager for IT Projects

- ucos在嵌入式芯片上的移植文档

- minix3源码,整个kernel的源代码,注释很全

- 数字图像处理与MATLAB实现

- 16位位图的算法和8位位图算法