Hynix 256Mbit Mobile DDR SDRAM: Overview & Specifications

需积分: 9 53 浏览量

更新于2024-07-23

收藏 1.28MB PDF 举报

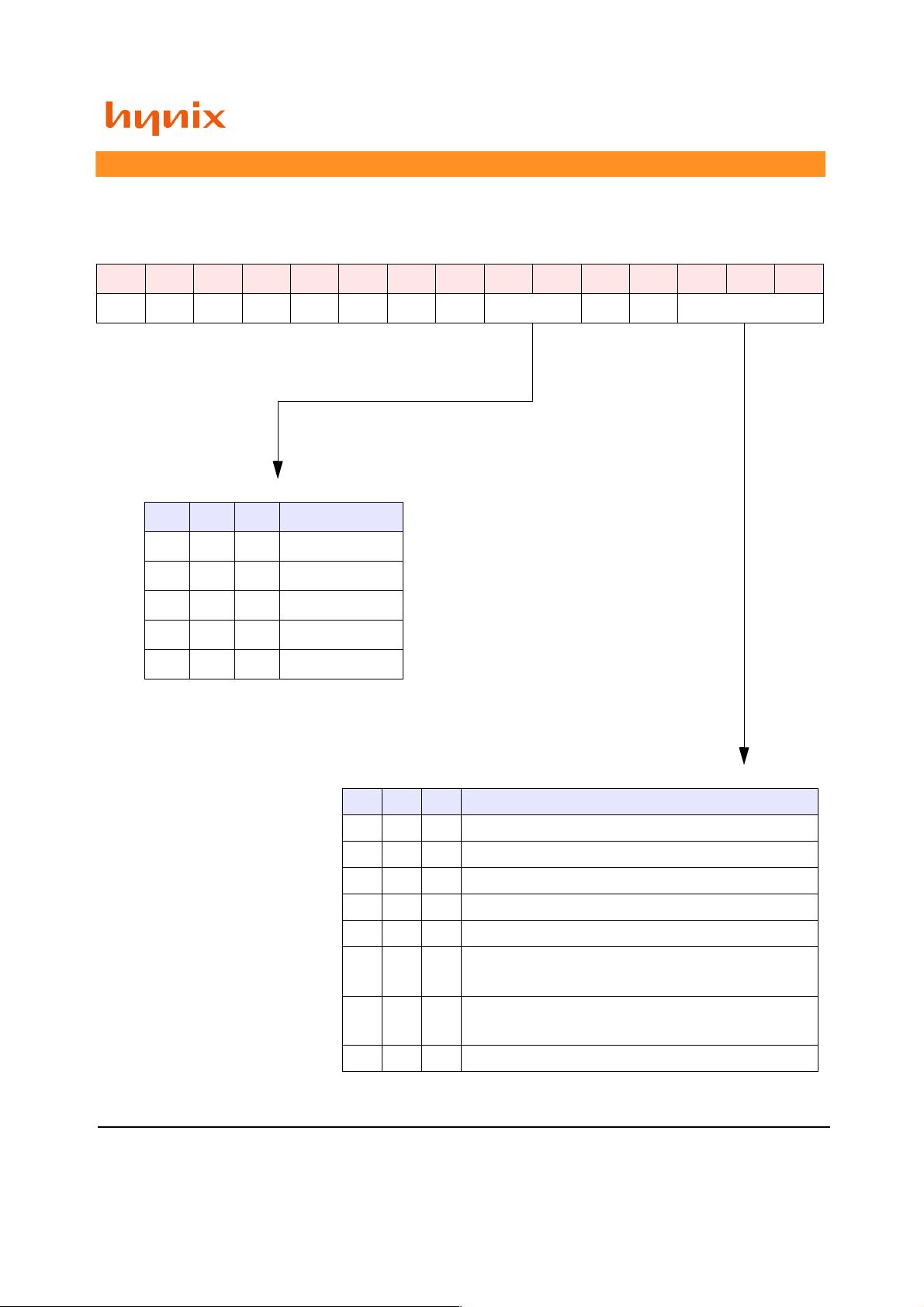

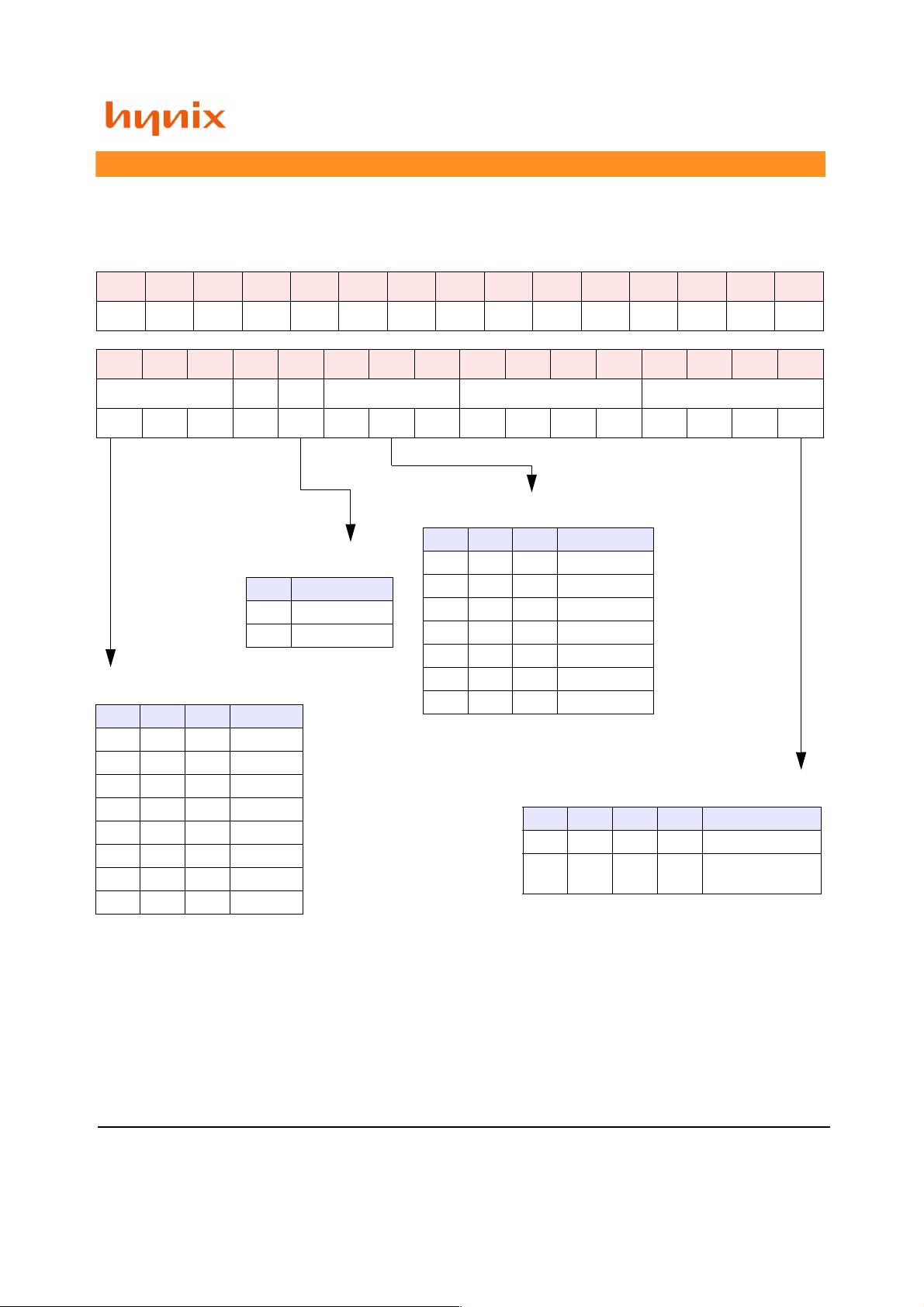

H5MS2562JFR是一款256Mbit的移动DDR SDRAM,它采用双数据速率(Double Data Rate, DDR)架构,这意味着在每个时钟周期内可以传输两次数据,显著提高了数据传输速度。该产品设计为x16的总线宽度,提供了高效的并行数据传输能力。

内存细胞阵列部分由四个独立的 banks 组成,每个 bank 内包含 4,194,304 个 16位单元,总共提供 4M x 4Bank x 16 I/O,支持大规模的数据存储和处理。这种设计结构确保了高密度和灵活性。

接口方面,H5MS2562JFR采用复用地址(Multiplexed Address),包括行地址和列地址的合并,简化了地址线的管理,提高了地址寻址的效率。此外,它支持双向数据 strobe(DQS),即LDQS和UDQS,它们与数据一起传输并在接收端用于捕获数据,确保了数据同步。

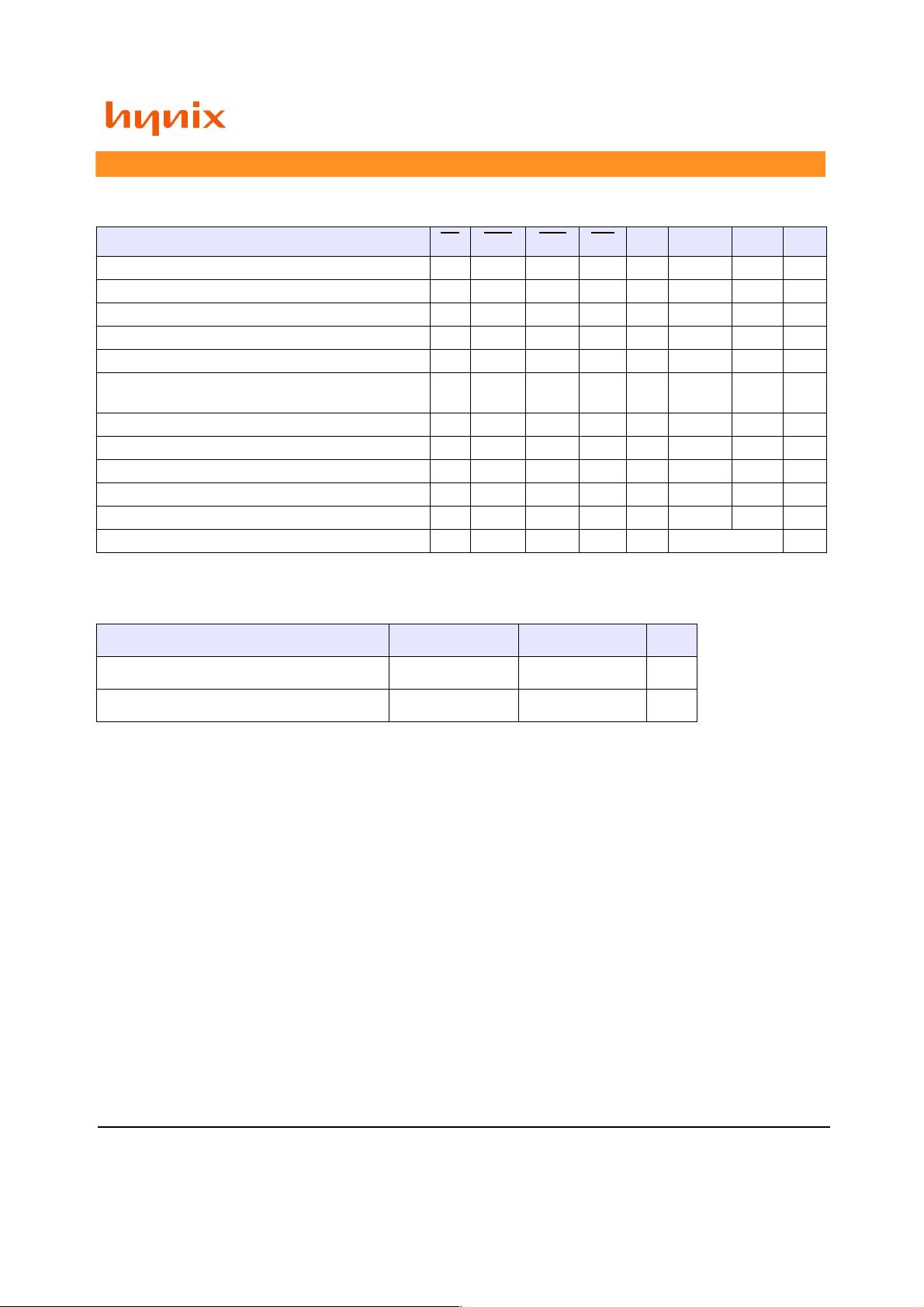

在低功耗特性上,该模块提供了多种节电模式,如 Partial Array Self Refresh (PASR) 和 Temperature Compensated Self Refresh (TCSR),能在不活跃期间保持部分内存区域处于低功耗状态。另外,还有 Drive Strength (DS) 调整选项和 Deep Power Down (DPD) 功能,后者作为可选特性,用户需联系Hynix办公室了解具体详情。

输入时钟采用差分信号,包括CK和CK两条线路,确保了稳定且低噪声的时钟信号传输。数据写入时,H5MS2562JFR支持数据mask功能,通过LDM和UDM输入信号,可以在数据 strobe 的上升和下降沿对写入数据进行屏蔽,增强了数据的安全性和可靠性。

值得注意的是,这份文档是Hynix公司的一份通用产品描述,可能会随着技术发展或市场需求的变化而更新,用户在使用时应参考最新版本。同时,Hynix公司并不承担电路使用责任,并且没有暗示任何专利许可。此文档的修订历史表明,它经历了多次迭代,从初步草稿到最终版本,不断完善和补充了相关信息。

2015-12-09 上传

2021-08-15 上传

2021-05-19 上传

2022-07-01 上传

2022-07-01 上传

2022-07-01 上传

2021-10-11 上传

gpscity

- 粉丝: 0

- 资源: 2

最新资源

- ES管理利器:ES Head工具详解

- Layui前端UI框架压缩包:轻量级的Web界面构建利器

- WPF 字体布局问题解决方法与应用案例

- 响应式网页布局教程:CSS实现全平台适配

- Windows平台Elasticsearch 8.10.2版发布

- ICEY开源小程序:定时显示极限值提醒

- MATLAB条形图绘制指南:从入门到进阶技巧全解析

- WPF实现任务管理器进程分组逻辑教程解析

- C#编程实现显卡硬件信息的获取方法

- 前端世界核心-HTML+CSS+JS团队服务网页模板开发

- 精选SQL面试题大汇总

- Nacos Server 1.2.1在Linux系统的安装包介绍

- 易语言MySQL支持库3.0#0版全新升级与使用指南

- 快乐足球响应式网页模板:前端开发全技能秘籍

- OpenEuler4.19内核发布:国产操作系统的里程碑

- Boyue Zheng的LeetCode Python解答集