DDR2 SDRAM操作详解:读写时序与初始化

"DDR2 读写时序与操作流程"

DDR2 SDRAM(Double Data Rate Second Synchronous Dynamic Random-Access Memory),是DDR内存的一种,它以两倍于时钟频率的速度传输数据,提升了内存性能。DDR2内存的读写时序是其核心操作的一部分,对于进行DDR2开发的工程师来说,理解这些时序至关重要。

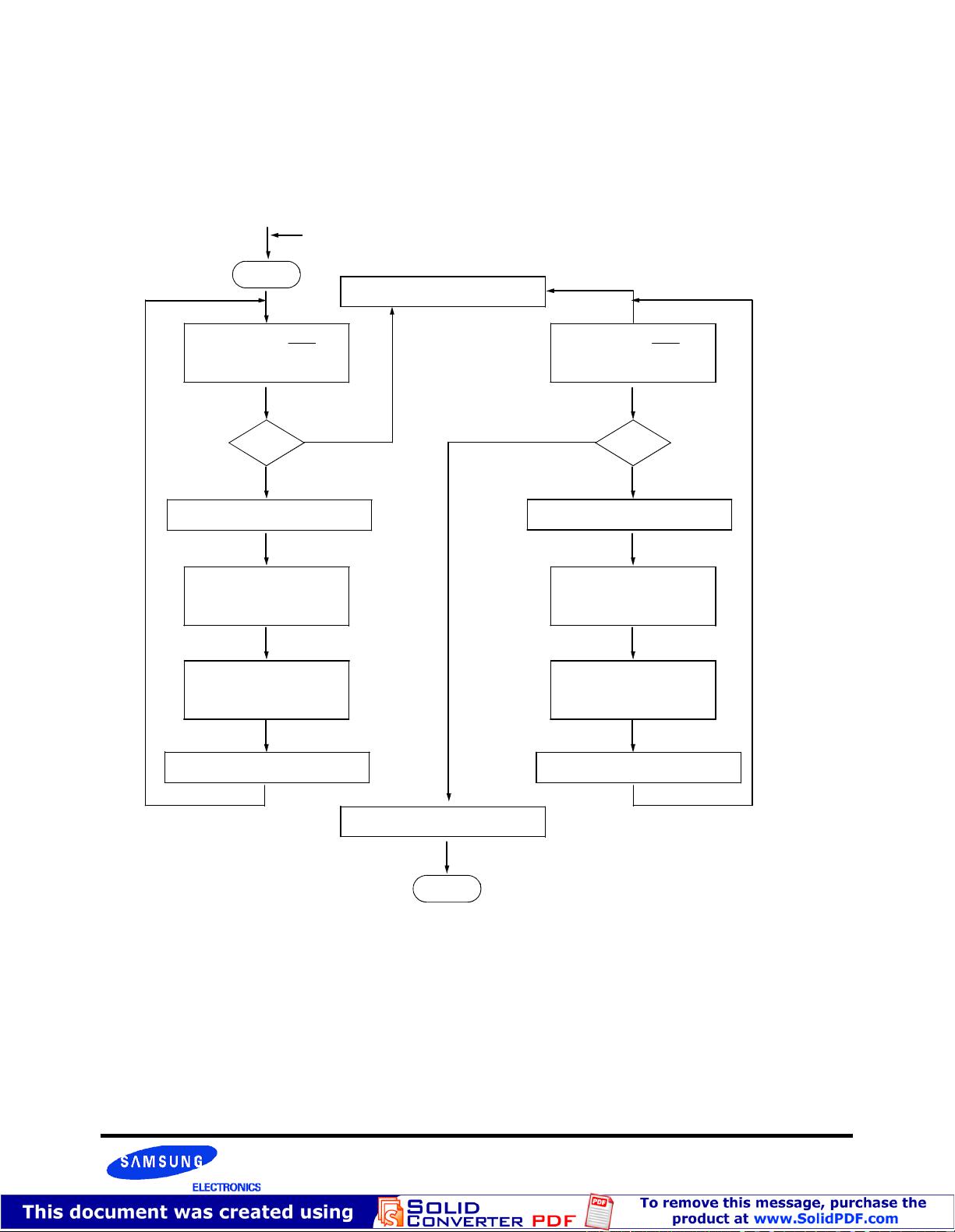

1. **操作时序规范**

DDR2 SDRAM的操作涉及多种状态转换,包括初始化、CKE(Clock Enable)的高低电平变化、激活(ACT)、预充电(PRE)、刷新(REF)、自我刷新(SRF)等。在DDR2内存中,CKE信号用于控制内存处于活动状态还是低功耗状态。当CKE为低电平时,内存进入断电状态;反之,当CKE为高电平时,内存恢复正常工作。

2. **基本功能**

- **初始化**:在使用DDR2 SDRAM之前,需要按照特定的时序进行初始化,包括CKEL(CKE低电平)和CKEH(CKE高电平)的设置,以及OCD(On-Die Termination)校准等步骤。

- **激活与预充电**:通过ACT命令激活内存行,同时通过BA0和BA1选择簇,A0至A13选定行。预充电命令PR(A)用于关闭所有簇的Bank,准备下一次操作。

- **读写操作**:读写操作基于突发模式,一次激活命令后,会按照设定的突发长度(BL4或BL8)连续读写。地址位包含起始列地址,决定读写顺序。读操作(RDA)和写操作(WRA)可能伴随自动预充电,提高效率。

- **(E)MRS**:设定(扩展)模式寄存器命令用于配置内存的工作参数,如CAS延迟、刷新周期等。

3. **突发模式与地址映射**

突发模式使得DDR2能连续访问多个相邻的存储单元,提高数据传输速率。地址位在读写命令中指定突发的起始列地址,根据突发长度自动进行后续列地址的递增。

4. **上电和初始化**

DDR2 SDRAM的上电和初始化非常关键,不正确的上电时序可能导致不可预期的行为。在上电过程中,需要保持CKE低于0.2*VDDQ(VDDQ是数据线电源电压)的一定时间,确保内部电路稳定。

5. **其他注意事项**

- 状态转换图并非详尽无遗,实际情况可能涉及更多簇、终结电阻的控制以及不同断电状态的处理。

- DDR2 SDRAM还有多种高级特性,如ODT(On-Die Termination)用于减少信号反射,ZQ(Zerosqueezing)引脚用于校准终端电阻等。

理解并掌握DDR2 SDRAM的读写时序和操作流程,对于高效地设计和优化内存系统至关重要,尤其是在嵌入式系统和高性能计算领域。开发者需关注内存的初始化、命令序列、时序约束,以及如何利用突发模式和自刷新等功能来提升系统性能。

懒惰马大哈

- 粉丝: 0

- 资源: 1

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性