ARMv8 Instruction Set Overview

PRD03-GENC-010197

Copyright © 2009-2011 ARM Limited. All rights reserved. Page 20 of 112

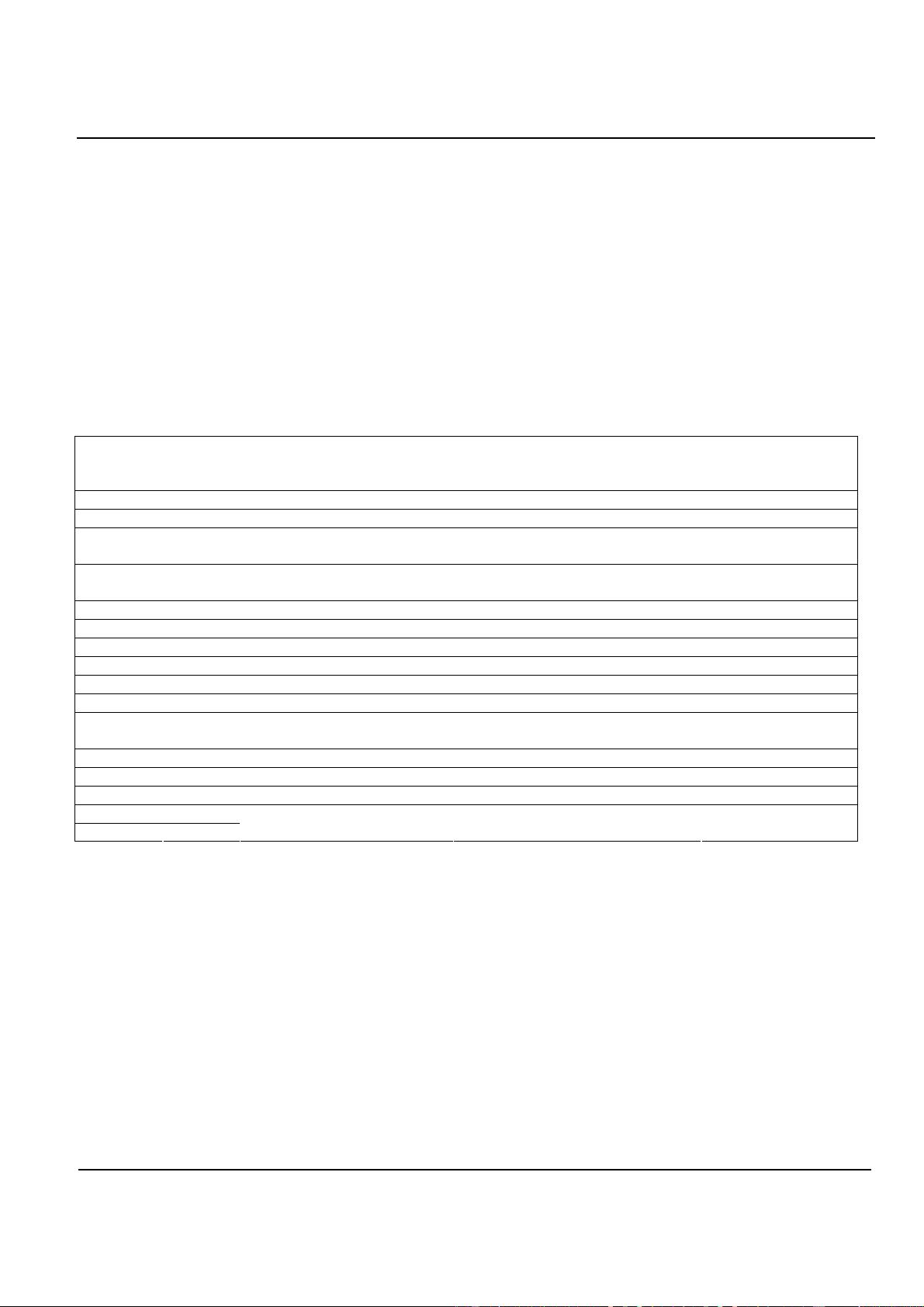

4.5 Load/Store Addressing Modes

Load/store addressing modes in the A64 instruction set broadly follows T32 consisting of a 64-bit base register

(Xn or SP) plus an immediate or register offset.

Type Immediate Offset

Register Offset Extended Register Offset

Simple register (exclusive)

[base{,#0}]

n/a n/a

Offset

[base{,#imm}] [base,Xm{,LSL #imm}] [base,Wm,(S|U)XTW {#imm}]

Pre-indexed

[base,#imm]!

n/a n/a

Post-indexed

[base],#imm

n/a n/a

PC-relative (literal) load

label

n/a n/a

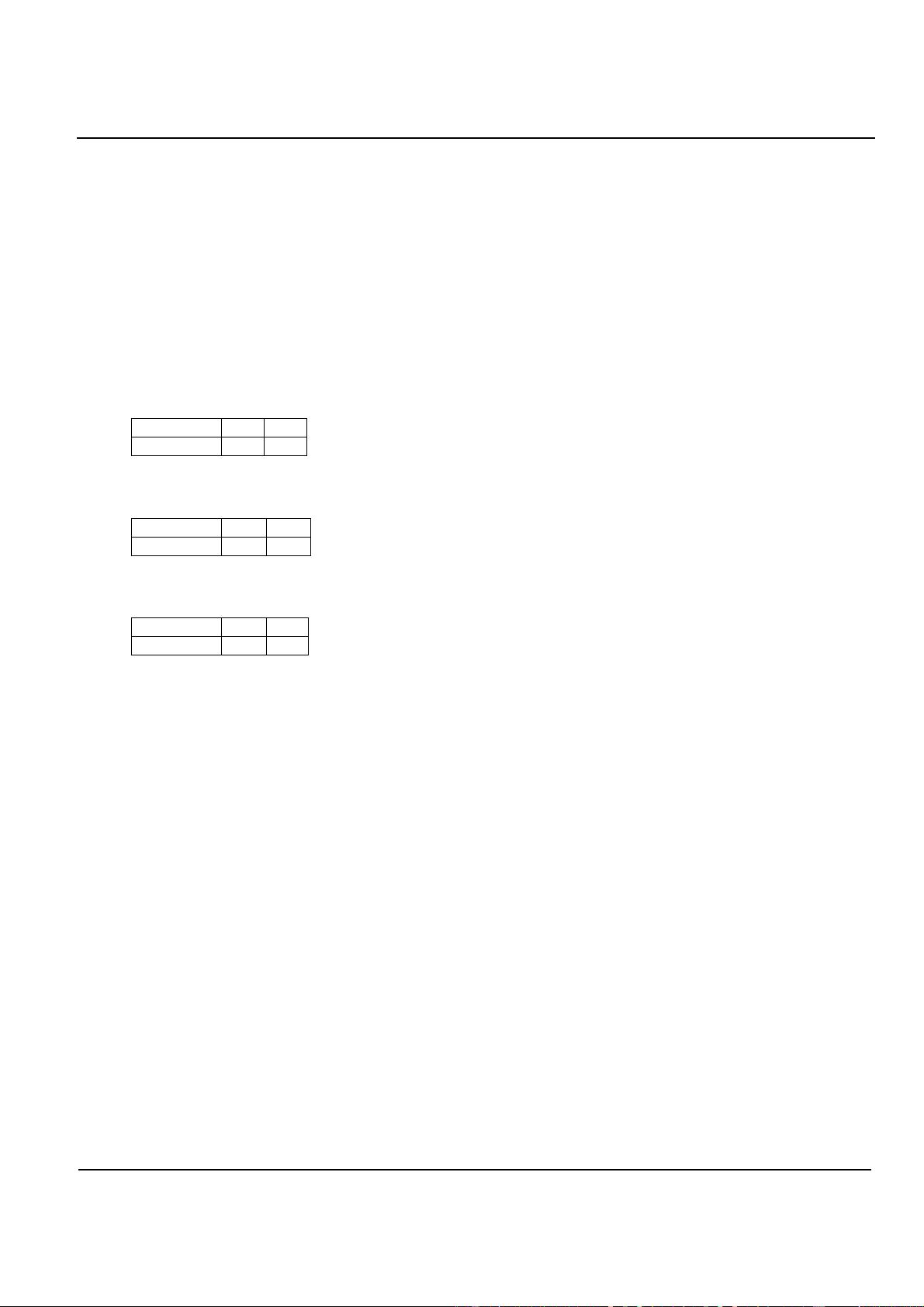

• An immediate offset is encoded in various ways, depending on the type of load/store instruction:

Bits Sign Scaling Write-

back?

Load/Store Type

0 -

- - exclusive / acquire / release

7 signed

scaled option register pair

9 signed

unscaled option single register

12 unsigned

scaled no single register

• Where an immediate offset is scaled, it is encoded as a multiple of the data access size (except PC-

relative loads, where it is always a word multiple). The assembler always accepts a byte offset, which is

converted to the scaled offset for encoding, and a disassembler decodes the scaled offset encoding and

displays it as a byte offset. The range of byte offsets supported therefore varies according to the type of

load/store instruction and the data access size.

• The "post-indexed" forms mean that the memory address is the base register value, then base plus

offset is written back to the base register.

• The "pre-indexed" forms mean that the memory address is the base register value plus offset, then the

computed address is written back to the base register.

• A “register offset” means that the memory address is the base register value plus the value of 64-bit index

register Xm optionally scaled by the access size (in bytes), i.e. shifted left by log2(size).

• An “extended register offset” means that the memory address is the base register value plus the value of

32-bit index register Wm, sign or zero extended to 64 bits, then optionally scaled by the access size.

• An assembler should accept Xm as an extended index register, though Wm is preferred.

• The pre/post-indexed forms are not available with a register offset.

• There is no "down" option, so subtraction from the base register requires a negative signed immediate

offset (two's complement) or a negative value in the index register.

• When the base register is SP the stack pointer is required to be quadword (16 byte, 128 bit) aligned prior

to the address calculation and write-backs – misalignment will cause a stack alignment fault. The stack

pointer may not be used as an index register.

• Use of the program counter (PC) as a base register is implicit in literal load instructions and not permitted

in other load or store instructions. Literal loads do not include byte and halfword forms. See section 5

below for the definition of label.