FPGA实现线性FIR数字滤波器设计与优化

版权申诉

36 浏览量

更新于2024-07-02

收藏 1.96MB DOC 举报

"基于FPGA实现线性FIR数字滤波器"

本文主要探讨的是如何在数字信号处理领域,特别是宽带信号处理中,利用现场可编程门阵列(FPGA)来实现线性FIR(有限冲击响应)数字滤波器。在宽带信号处理中,目标检测和分类依赖于对回波的频谱特性分析,这通常需要精确的滤波操作。FIR滤波器因其可灵活调整参数以适应不同频率段的需求,以及易于实现线性相位和稳定性,成为理想的解决方案。

FIR滤波器设计的核心在于其乘加运算,这是滤波过程中的关键步骤。文中提出了一种利用分布式算法和查找表结构的FPGA实现方法。查找表用于简化乘法运算,通过将乘法转换为查表,可以降低对存储容量的需求,同时利用多级流水线技术,可以在不牺牲系统速度的情况下,提高处理效率。VHDL语言被选为实现这一设计方案的编程工具,它是一种硬件描述语言,适用于FPGA的设计和验证。

文章的结构分为以下几个部分:

1. 绪论:这部分介绍了课题的背景和意义。背景可能涉及宽带信号处理技术的重要性,以及FPGA在高速数字信号处理中的作用。课题的意义可能包括提高滤波器设计的灵活性、效率和成本效益。

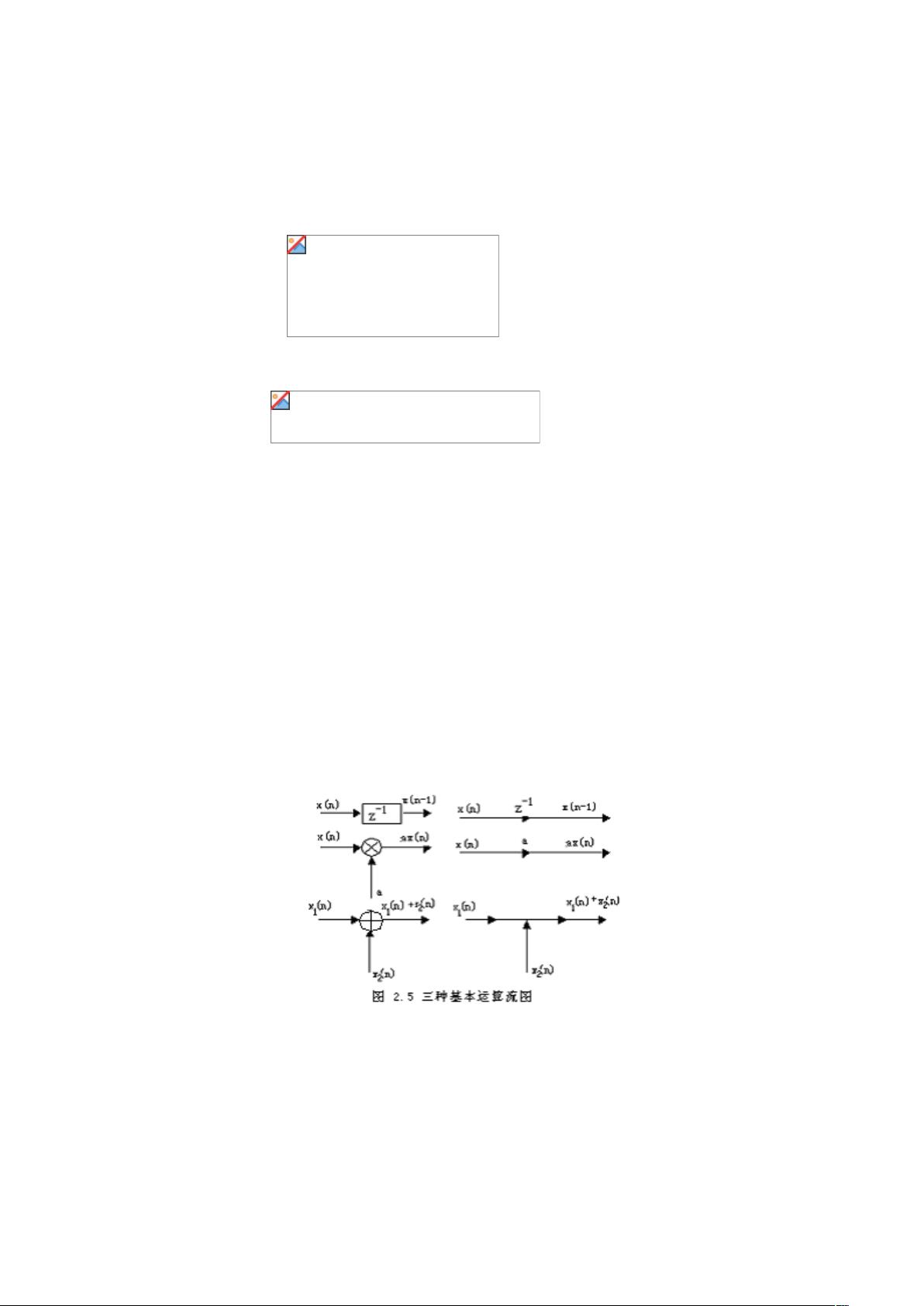

2. 滤波器设计原理:这一部分详细解释了滤波器的基本概念,包括滤波原理、滤波器的分类,以及数字滤波器结构的不同表示方法。这些基础知识为后续的FIR滤波器设计提供了理论基础。

3. 有限冲击响应(FIR)滤波器的基本概念:这部分深入阐述了FIR滤波器的特点,比如线性相位、稳定的频率响应和可设计的脉冲响应等,这些都是FIR滤波器在实际应用中受到青睐的原因。

4. FIR数字滤波器的设计思路:这部分将介绍如何利用FPGA的并行处理能力,结合分布式算法和查找表技术,设计出高效、灵活的FIR滤波器。多级流水线技术的应用也将在此部分详细阐述,以展示如何优化计算性能。

整篇文章旨在为读者提供一个基于FPGA实现线性FIR滤波器的全面设计流程,涵盖了理论基础、设计方法和实现技术,对于理解和应用FPGA在数字信号处理领域的滤波器设计具有重要的参考价值。

2023-06-20 上传

2023-06-20 上传

2021-09-18 上传

2021-10-05 上传

2021-10-04 上传

2021-10-03 上传

2021-09-28 上传

2021-09-18 上传

2021-10-06 上传

智慧安全方案

- 粉丝: 3797

- 资源: 59万+

最新资源

- 掌握压缩文件管理:2工作.zip文件使用指南

- 易语言动态版置入代码技术解析

- C语言编程实现电脑系统测试工具开发

- Wireshark 64位:全面网络协议分析器,支持Unix和Windows

- QtSingleApplication: 确保单一实例运行的高效库

- 深入了解Go语言的解析器组合器PARC

- Apycula包安装与使用指南

- AkerAutoSetup安装包使用指南

- Arduino Due实现VR耳机的设计与编程

- DependencySwizzler: Xamarin iOS 库实现故事板 UIViewControllers 依赖注入

- Apycula包发布说明与下载指南

- 创建可拖动交互式图表界面的ampersand-touch-charts

- CMake项目入门:创建简单的C++项目

- AksharaJaana-*.*.*.*安装包说明与下载

- Arduino天气时钟项目:源代码及DHT22库文件解析

- MediaPlayer_server:控制媒体播放器的高级服务器