"Verilog算法及建模方法的综合文档"

下载需积分: 9 | DOC格式 | 282KB |

更新于2024-01-03

| 74 浏览量 | 举报

Verilog算法及建模整理文档是一份综合性的文档,旨在介绍Verilog算法的建模方法。Verilog是一种硬件描述语言,用于描述数字系统的行为和结构。本文档详细介绍了Verilog算法的概念、语法和使用方法。

Verilog算法是一种用于描述数字电路行为和结构的语言。它采用了类似于C语言的语法结构,具有模块化和层次化的设计风格。与其他硬件描述语言相比,Verilog具有更高的抽象层次,可以更方便地进行系统级设计和验证。

本文档首先介绍了Verilog算法的基本概念和建模方法。Verilog模块是Verilog程序的基本单位,用于描述数字系统中的各个功能块。一个Verilog模块包含了输入输出端口、内部信号和行为描述。行为描述使用类似于C语言的语法结构,包括赋值语句、条件语句和循环语句等。

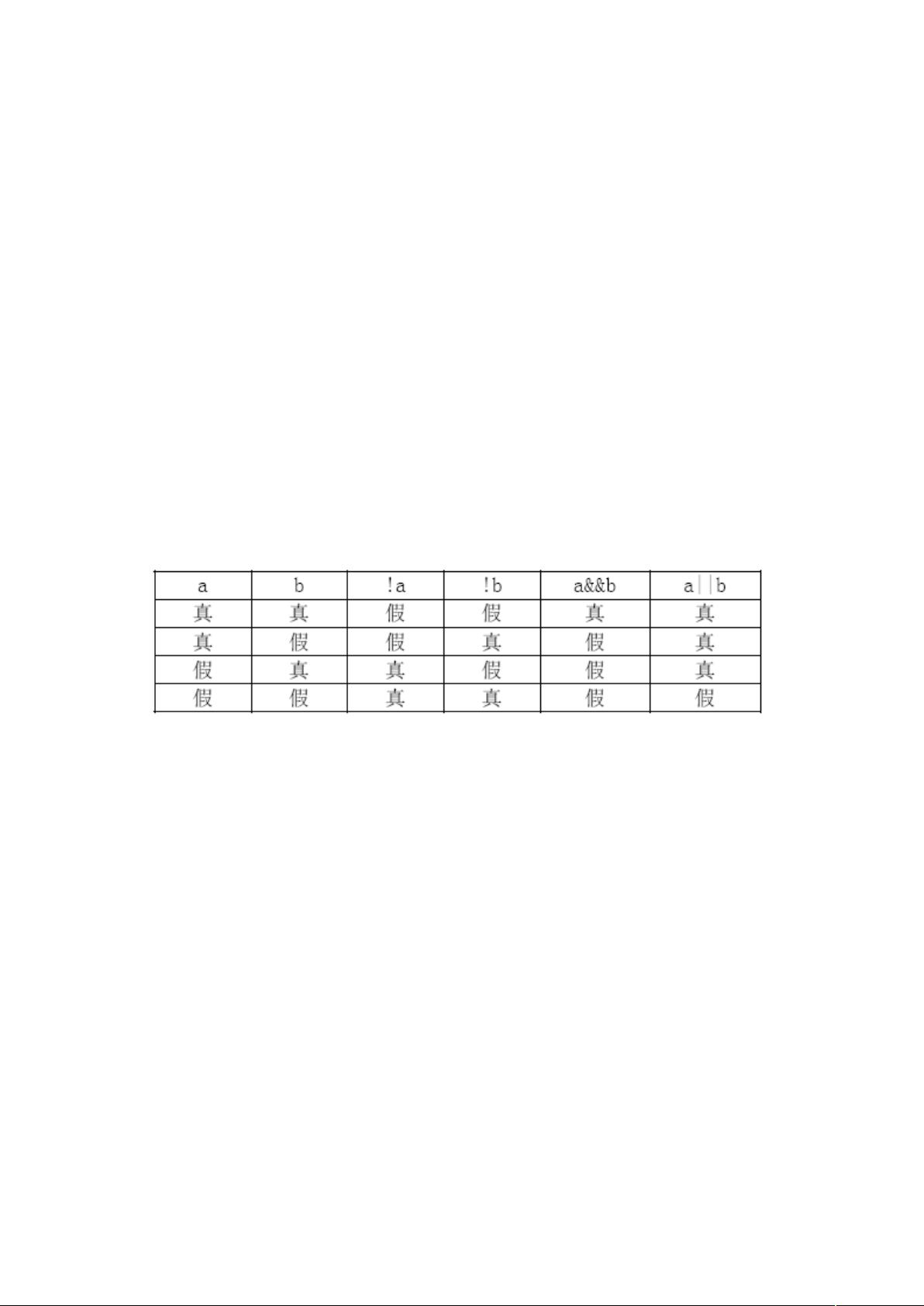

接下来,本文档详细介绍了Verilog算法的语法和使用方法。Verilog语法包括了常用的数据类型、运算符、控制语句和模块实例化等,在写Verilog程序时需要遵循这些语法规则。同时,本文档还介绍了Verilog的一些高级特性,如层次化设计、时序建模和模块重用等,这些特性可以帮助开发者更高效地进行Verilog算法的设计和实现。

此外,本文档还对Verilog与其他语言进行了比较。与C语言相比,Verilog具有更多的硬件描述特性,可以更方便地进行数字系统的建模和仿真。与VHDL(VHSIC Hardware Description Language)相比,Verilog更简洁、更易学,更适用于快速原型开发和系统级设计。

总之,Verilog算法及建模整理文档提供了一份全面的Verilog算法学习和参考资料。它介绍了Verilog算法的基本概念和建模方法,并详细介绍了Verilog的语法和使用方法。本文档还比较了Verilog与其他语言的异同,帮助读者更好地理解Verilog算法的特点和应用场景。无论是初学者还是有经验的Verilog开发者,都可以从本文档中获得有价值的指导和启发。

相关推荐

Chenlianxinong

- 粉丝: 3

最新资源

- 革新操作体验:无需最小化按钮的窗口快速最小化工具

- VFP9编程实现EXCEL操作辅助软件的使用指南

- Apache CXF 2.2.9版本特性及资源下载指南

- Android黄金矿工游戏核心逻辑揭秘

- SQLyog企业版激活方法及文件结构解析

- PHP Flash投票系统源码及学习项目资源v1.2

- lhgDialog-4.2.0:轻量级且美观的弹窗组件,多皮肤支持

- ReactiveMaps:React组件库实现地图实时更新功能

- U盘硬件设计全方位学习资料

- Codice:一站式在线笔记与任务管理解决方案

- MyBatis自动生成POJO和Mapper工具类的介绍与应用

- 学生选课系统设计模版与概要设计指南

- radiusmanager 3.9.0 中文包发布

- 7LOG v1.0 正式版:多元技术项目源码包

- Newtonsoft.Json.dll 6.0版本:序列化与反序列化新突破

- Android实现SQLite数据库高效分页加载技巧