Xilinx UltraFast设计方法论:Vivado设计流程优化指南

需积分: 9 119 浏览量

更新于2024-07-17

收藏 10.22MB PDF 举报

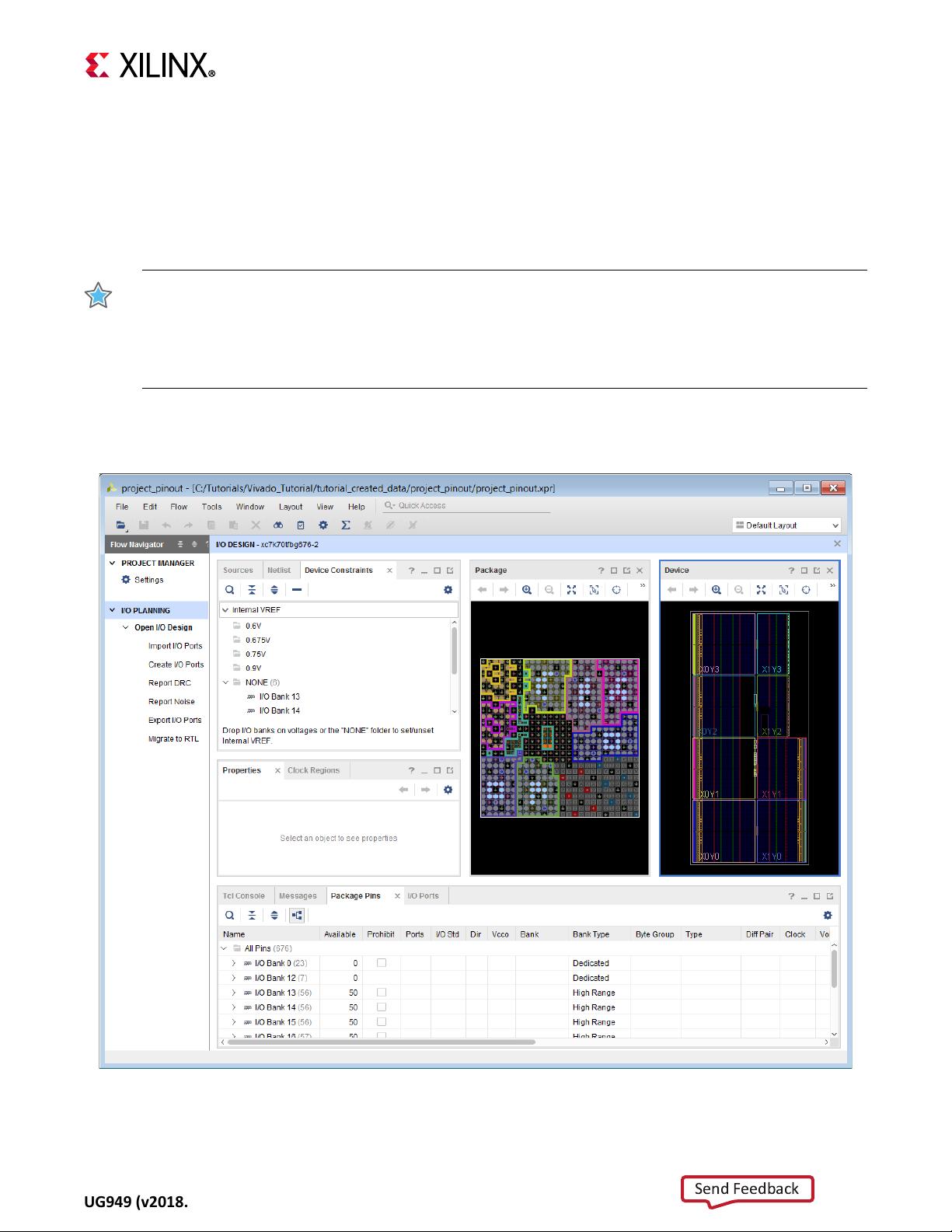

本资源是一份名为"Xilinx® UltraFast™ 设计方法论指南"的文档(UG949),专为VIVADO FPGA设计者提供最佳实践。VIVADO是一款由Xilinx公司开发的FPGA设计工具套件,旨在帮助设计师高效地进行现代FPGA设计流程。随着设计规模的增大和复杂性的提升,该方法论强调了在设计过程中的各个阶段执行特定步骤和任务的重要性,以确保设计的成功。

主要内容包括以下几个关键部分:

1. **概述与更新**:

- UG949文档的2018.2版本更新了Tcl命令,反映了复用(replication)默认启用,去除了以前需要使用的`-fanout_opt`选项。

- 新增了与HBM设备设计、软SLR地板平面约束使用、SLR交叉寄存器等内容的章节,反映了针对新硬件特性的支持。

2. **特定设计策略**:

- **Cascaded Clock Buffers**:介绍了关于不要随意修改(DONT_TOUCH)属性的注意事项。

- **Clock Domain Crossing**:提供了关于时钟域穿越(CDC)违例豁免的提示,帮助处理时钟同步问题。

- **Reviewing and Cleaning DRCs**:有关于DRC违例豁免的建议,有助于解决设计规则检查(DRC)中的错误。

- **Running Report Methodology**:对于报告方法论,提到RAM和DSP算子的可选流水线处理,以及对方法论检查违例豁免的提示。

3. **实时操作指南**:

- **Route Runtime**:新增了一个章节,可能涉及实时路由策略和优化。

4. **高级主题**:

- **Designing with HBM Devices**:这部分专注于高性能内存(HBM)设备的设计,可能涉及到接口和性能优化。

- **Using Soft SLR Floorplan Constraints**:讲解如何利用软件定义的SLR布局约束来管理资源分配。

- **Using SLR Crossing Registers**:探讨如何有效地管理系统级跨时钟区域(SLR)的数据通信。

遵循这份UltraFast Design Methodology Guide,设计师能够更有效地利用VIVADO工具,缩短设计时间,同时保证设计质量和稳定性。不断更新的文档确保了与最新VIVADO版本的兼容性,并针对新技术提供了相应的指导。设计师在实际操作中,应结合具体项目需求,逐步学习并应用这些最佳实践。

2020-08-23 上传

2021-03-23 上传

2023-08-02 上传

2023-08-01 上传

2023-07-28 上传

2023-08-01 上传

2023-07-25 上传

2023-10-12 上传

flywind7

- 粉丝: 0

- 资源: 6

最新资源

- 批量文件重命名神器:HaoZipRename使用技巧

- 简洁注册登录界面设计与代码实现

- 掌握Python字符串处理与正则表达式技巧

- YOLOv5模块改进 - C3与RFAConv融合增强空间特征

- 基于EasyX的C语言打字小游戏开发教程

- 前端项目作业资源包:完整可复现的开发经验分享

- 三菱PLC与组态王实现加热炉温度智能控制

- 使用Go语言通过Consul实现Prometheus监控服务自动注册

- 深入解析Python进程与线程的并发机制

- 小波神经网络均衡算法:MATLAB仿真及信道模型对比

- PHP 8.3 中文版官方手册(CHM格式)

- SSM框架+Layuimini的酒店管理系统开发教程

- 基于SpringBoot和Vue的招聘平台完整设计与实现教程

- 移动商品推荐系统:APP设计与实现

- JAVA代码生成器:一站式后台系统快速搭建解决方案

- JSP驾校预约管理系统设计与SSM框架结合案例解析