Quartus II FPGA时序约束:Tsu/Tco解析与优化

18 浏览量

更新于2024-08-31

收藏 605KB PDF 举报

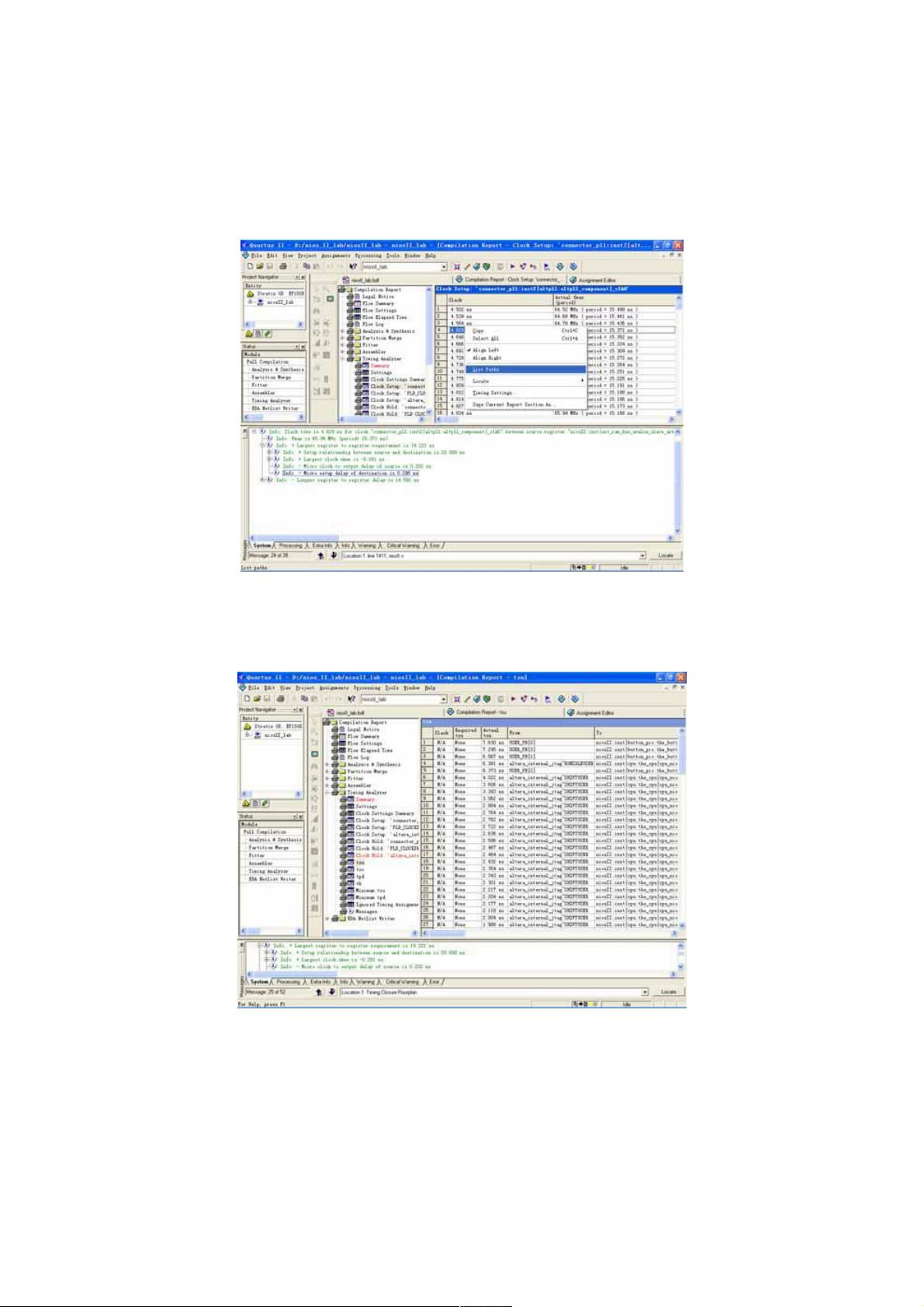

"Quartus II 中Tsu/Tco 的约束方法主要涉及FPGA设计中的时序分析和优化。Tsu (Setup Time) 和 Tco (Output Clock to Output Data) 是衡量数字电路中时钟与数据关系的重要参数,它们直接影响到系统的工作性能和稳定性。在Quartus II 中,可以通过\"List Paths\"命令来检查这些参数,以确保设计满足严格的时序要求。

1. Tsu/Tco 在片内:

Tsu/Tco 主要取决于 FPGA 器件的工艺,通常在几百ps级别。由于工艺、温度和电源电压的影响,这些值在运行时可能会有所变化。通过\"List Paths\"可以观察到这些关键路径,以了解设计中可能存在的时序问题。

2. Tsu/Tco 在管脚上:

在系统级,管脚上的 Tsu/Tco 对于保证不同芯片间的同步通信至关重要。例如,在100MHz的工作频率下,两个芯片之间的通信必须确保信号传输的总延迟不超过10ns。这意味着,如果信号作为FPGA的输入,前级芯片的Tco应加上FPGA的Tsu不超过10ns;若作为输出,则FPGA的Tco加上后级芯片的Tsu同样不能超过10ns。

- IOE走线的延迟:Altera的FPGA在输入和输出管脚上使用Fast Input Register和Fast Output Register来优化Tsu和Tco,降低延迟。

- 内部逻辑走线的延迟:FPGA的布线资源,如C4、C8、C16等,决定了信号在内部传输的延迟,这取决于不同LAB间的走线长度。

- 触发器的Tsu/Tco:这些参数由器件工艺决定,并在实际运行中会因环境因素(如温度和电压)略有变化。

3. 解决时序约束问题:

当遇到时序问题时,Quartus II 提供了一系列工具和方法来解决,包括时序分析、路径优化、时钟树综合(CTS)以及使用更高级的时序约束技术。理解并正确应用这些工具是确保FPGA设计成功的关键。

理解和管理Tsu/Tco在Quartus II 中的约束对于实现高效、可靠的FPGA设计至关重要。设计师需要密切关注这些参数,并在设计流程中进行持续的时序分析和优化,以保证设计在各种工作条件下都能稳定运行。"

2010-01-19 上传

678 浏览量

167 浏览量

436 浏览量

138 浏览量

353 浏览量

217 浏览量

点击了解资源详情

点击了解资源详情

weixin_38628429

- 粉丝: 7

最新资源

- 初学者入门必备!Visual C++开发的连连看小程序

- C#实现SqlServer分页存储过程示例分析

- 西门子工业网络通信例程解读与实践

- JavaScript实现表格变色与选中效果指南

- MVP与Retrofit2.0相结合的登录示例教程

- MFC实现透明泡泡效果与文件操作教程

- 探索Delphi ERP框架的核心功能与应用案例

- 爱尔兰COVID-19案例数据分析与可视化

- 提升效率的三维石头制作插件

- 人脸C++识别系统实现:源码与测试包

- MishMash Hackathon:Python编程马拉松盛事

- JavaScript Switch语句练习指南:简洁注释详解

- C语言实现的通讯录管理系统设计教程

- ASP.net实现用户登录注册功能模块详解

- 吉时利2000数据读取与分析教程

- 钻石画软件:从设计到生产的高效解决方案