High-bandwidth Digital Content Protection System 8 July 2009

Revision 1.4 Digital Content Protection LLC

Page 15 of 90

depending upon whether ADVANCE_CIPHER mode is enabled (see below). However, the frame counter

does not advance while the HDCP device is in the HDMI AVMUTE state, and does not resume advancing

after HDMI AVMUTE state until the first encrypted frame. K

i

is a 56-bit key used to initialize the HDCP

cipher for encryption or decryption of the HDCP Content. M

i

is a new 64-bit initialization value for the

HDCP cipher. R

i

is a 16-bit value used for link integrity verification, and is updated for every 128

th

frame

counter increment, starting with the 128

th

. The HDCP Transmitter verifies R

i

' against its own calculations to

insure that the video receiver is still able to correctly decrypt the information. This verification is made at a

minimum rate of once every two seconds. Synchronous reading of Ri every time it changes (every 128

th

frame) is also acceptable in lieu of asynchronous polling. (Synchronous reading in the frame prior to Ri

update and shortly after 1 millisecond of the Ri update also provides a method of detecting frame counter

mismatch between HDCP transmitter and HDCP receiver when either device does not support Enhanced

Link Verification). It is required that the R

i

' read operation complete within 1 milliseconds from the time

that it is initiated by the HDCP Transmitter. Failure for any reason causes the HDCP Transmitter to

consider the HDCP Receiver to be unauthenticated.

In order to enhance the detection of the loss of encryption synchronization, the HDCP Transmitter and

Receiver may optionally support Enhanced Link Verification, in which a computation to aid verification of

cipher synchronization is performed when a specific video pixel is processed. For every 16

th

frame counter

increment, the decrypted value of channel zero of the first pixel is combined with the least significant byte

Rj using the XOR operation, and the result is made available on the Pj port. If this feature is supported by

an HDCP Receiver, the Bcaps bit 1.1_FEATURES is set and the Pj’ port is always updated. The HDCP

Transmitter may optionally support reading and verifying the Pj’ value against an internally generated Pj

value. However, unless a minimum of three successive mismatches of stable values occur, this is

considered to be a pixel transmission error and not an authentication or synchronization error. In addition,

the mismatched Pj values must be sampled more than once in the same manner as the Ri value. (see

Appendix C). Note that the frame counter may advance on unencrypted frames if ADVANCE_CIPHER

mode (see below) is enabled, in which case the least significant byte Rj and the pixel data is captured every

16

th

frame. However, if ADVANCE_CIPHER is not enabled, these values are updated on every 16

th

encrypted frame.

ADVANCE_CIPHER mode is an optional mode in which the cipher state and frame counter is advanced

for every frame in DVI mode, or for every frame when not in AVMUTE state for HDMI mode, regardless

of whether encryption is enabled or disabled. The HDCP Receiver indicates this capability by setting the

1.1_FEATURES Bcaps bit, and the HDCP Transmitters enables it by setting the

ENABLE_1.1_FEATURES bit in the Ainfo byte. The frame counter is first updated to a value of 1 when

the first ENC_EN is sent or received after authentication, and thereafter incremented every frame, until

SET_AVMUTE is set (in HDMI mode). The cipher state is not advanced if HDMI mode AV_MUTE is

active, and resumes advancing with the first ENC_EN frame after HDMI CLEAR_AVMUTE.

Note: An HDMI-capable HDCP Transmitter that has enabled AC (by writing 1 to

ENABLE_1.1_FEATURES bit of AInfo) may need to re-authenticate after sending an AVMUTE to the

HDCP Receiver, since the HDCP Receiver may have ignored the HDMI General Control Packet that

contained the Set_AVMUTE command, causing the loss of HDCP cipher synchronization.

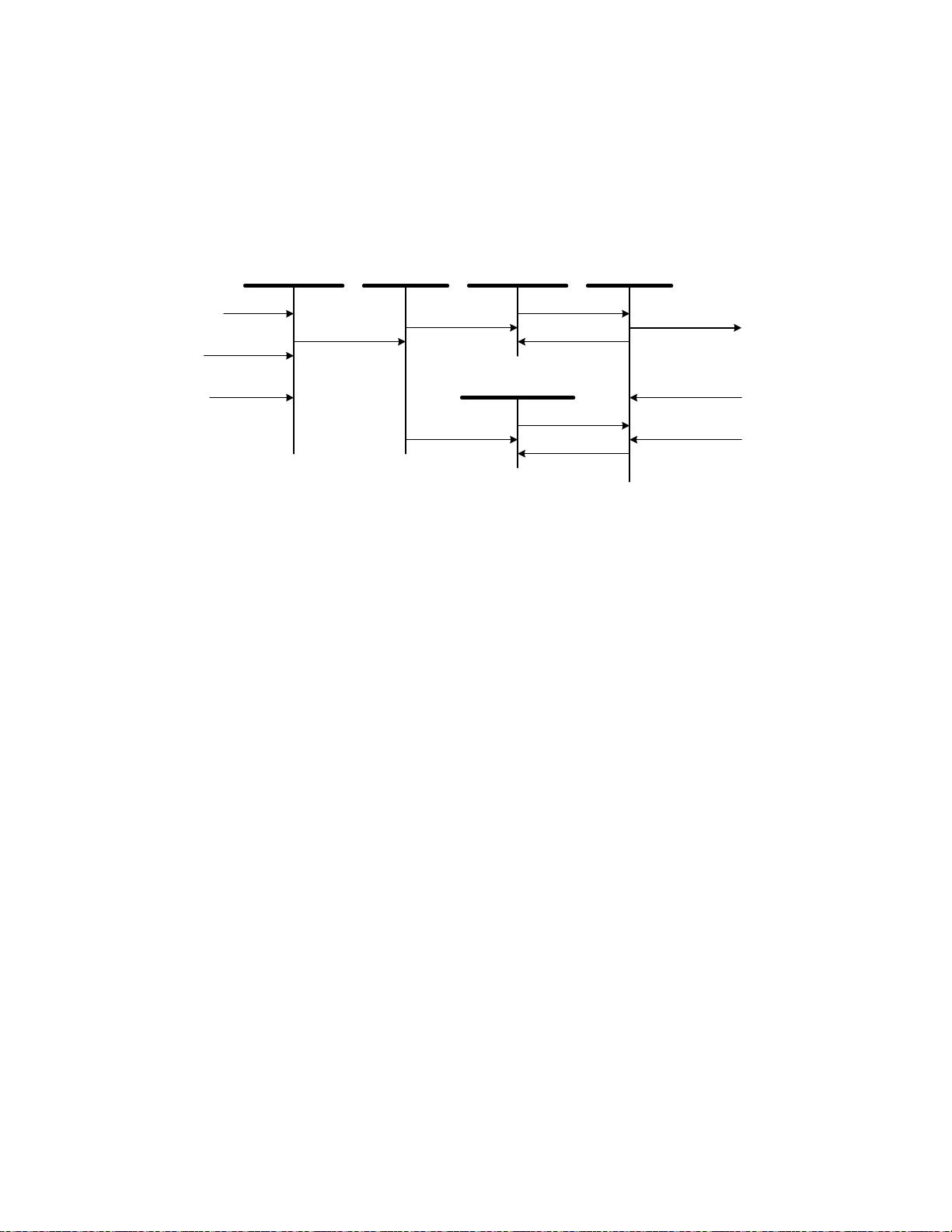

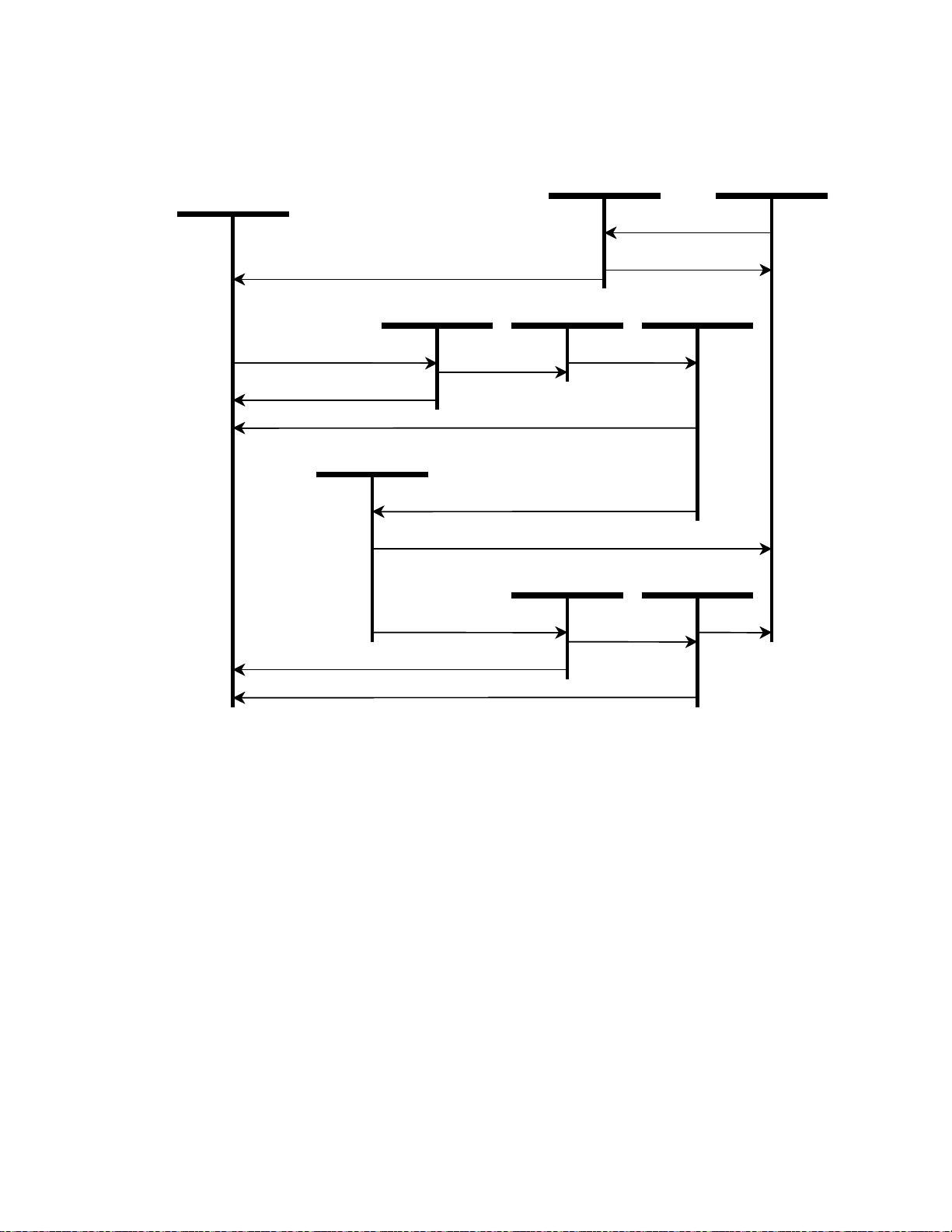

2.3 HDCP Transmitter State Diagram

The HDCP Transmitter Link State Diagram and HDCP Transmitter Authentication Protocol

State Diagram (Figures 2-5 and 2-6) illustrate the operation states of the authentication

protocol for an HDCP Transmitter that is not an HDCP Repeater. For HDCP Repeaters, the

downstream (HDCP Transmitter) side is covered in Section 2.5.

A variety of events are involved in the transmitter’s decision to begin authentication or to

transmit video. Some examples of such events may include HDCP_HPD (HDCP Hot Plug

Detect) of an attached HDCP Receiver, completion of certain phases of the operating system,

a software request, and mode settings. HDCP receivers are not required to authenticate until

presented with a video signal. When an HDCP Receiver acknowledges an I

2

C register read, it