TI TLV320DAC3100: 低功耗音频D/A转换器与数字处理技术详解

需积分: 10 142 浏览量

更新于2024-06-28

4

收藏 2.4MB PDF 举报

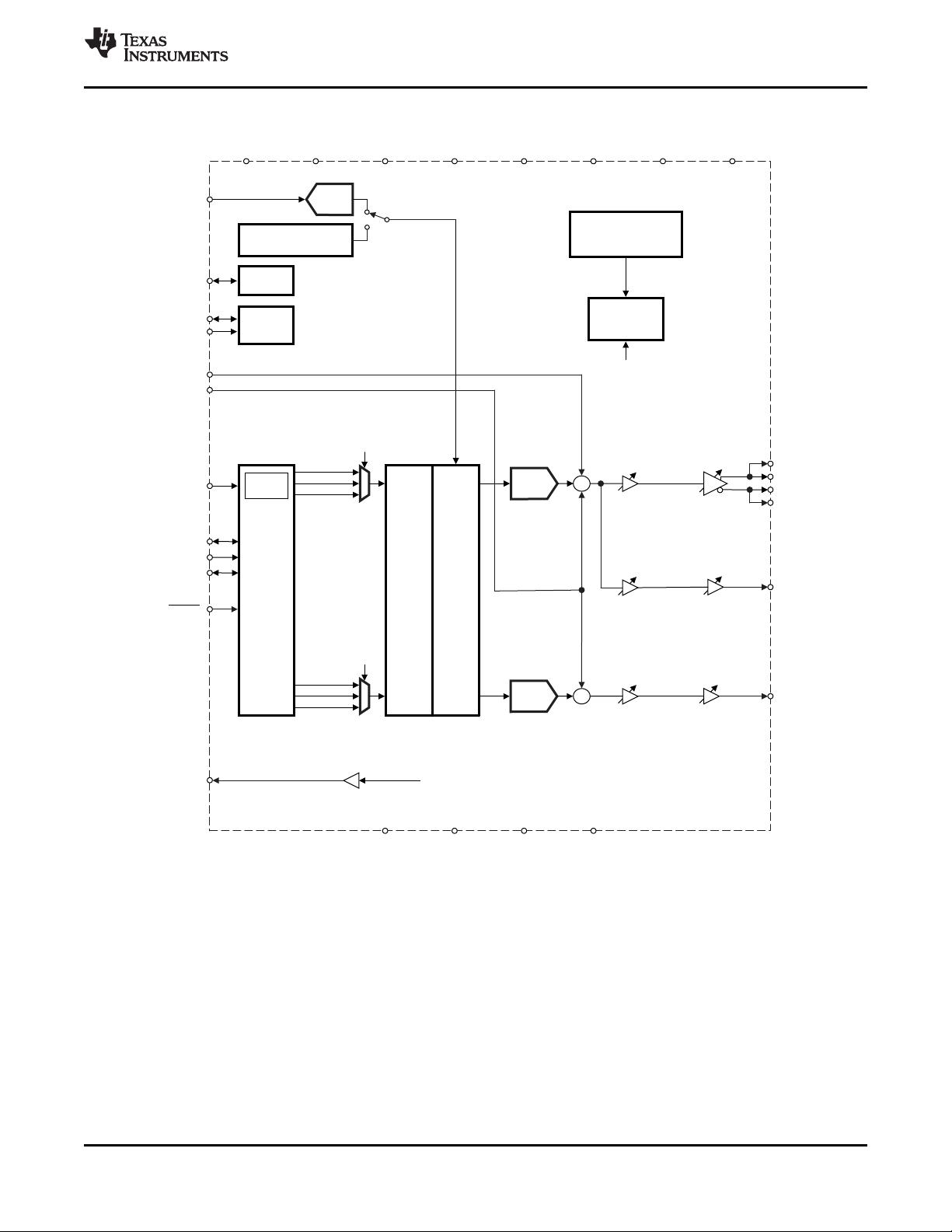

TI-TLV320DAC3100是一款针对低功耗音频应用的多功能数字模拟转换器(DAC),它在音频处理和单声道类-DSpeaker放大器方面表现出色。该设备的主要特点包括:

1. **高保真度**:TLV320DAC3100提供了95分贝的信噪比(SNR),确保了音频信号的清晰度和纯净度。

2. **宽广的采样率支持**:它兼容8千赫兹到192千赫兹的多种采样率,适应不同音频源的输入需求,适用于各种音频播放场景。

3. **音频输出能力**:设备内置一个2.5瓦或1.6瓦的单声道类-D音箱驱动器,支持4欧姆或8欧姆阻抗,满足不同负载下的音频输出。

4. **多通道输入**:拥有两个单端输入,具备混合功能,并提供输出电平控制,便于音频信号的合成和调整。

5. **多种输出选项**:除了立体声耳机/线路输出外,还有单声道类-D音箱输出,以及用于监听的接口。

6. **内置音频处理功能**:内置25个数字音频处理块(PRB_P1至PRB_P25),可实现各种滤波器(如biquad和FIR滤波)、动态范围控制器(DRC)和三维结构处理,增强了音频质量与动态效果。

7. **数字混音技术**:支持数字混音,能够灵活地结合多个音频源,便于音频信号的实时处理。

8. **控制灵活性**:通过Pin Controlor Register提供数字播放时的音量控制设置,便于用户个性化定制。

9. **辅助功能**:内置数字正弦波发生器,可用于产生提示音或按键点击音,提升用户体验。

10. **安全性和法律声明**:文档末尾包含重要的注意事项,涉及产品可用性、保修政策、在安全关键应用中的使用限制、知识产权声明及其它免责声明,确保用户在实际应用中的合规性和风险意识。

这款TLV320DAC3100旨在为音频系统设计师提供强大的性能和灵活性,尤其适合需要高质量音频输出和音频处理功能的应用,例如便携式音频设备、家用音频系统和汽车音响等。开发者在使用时应确保了解并遵循所有相关注意事项,以确保产品的可靠性和性能。

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

不觉明了

- 粉丝: 4533

- 资源: 5759

最新资源

- thread_analysis:JDK中JUC学习记录

- list.rar_Visual_C++_

- dotfiles:点文件

- Scratch少儿编程项目音效音乐素材-【水】相关音效-沼泽.zip

- CombineBitmap.zip

- 软件测试方向答案及试题.7z

- cat-angular-demo:一个演示项目,展示了猫形角结合弹簧靴的用法

- Scratch少儿编程项目音效音乐素材-【事件】声音-魔术.zip

- Fiji-ImageJ-科研与工程研发成像软件

- 【音乐模块开源】某易云、某狗、mi咕、某Q、某我,部分支持无损音质-易语言

- code.txt.zip_Windows编程_C++_Builder_

- a_python_

- BotFramework:这个POC就是关于使用BOT框架创建聊天机器人的,逐步说明提供了创建第一个BOT的方法

- LED-animator:已弃用–用于Arduino上NeoPixel和Dotstar LED的动画工具

- Gustow:Android的互动餐厅菜单

- 一波实用的图片处理算法.适用于二值化 验证码 图色分离 图片美化.纯源码-易语言