数字逻辑实验:二进制加法器设计与Logisim仿真

需积分: 0 161 浏览量

更新于2024-06-30

收藏 468KB DOCX 举报

"华中科技大学的数字逻辑实验课程,主要涉及二进制加法器的设计与仿真,使用Logisim软件进行验证。实验目标是通过设计五种不同的加法器,包括半加器、全加器、串行进位的四位并行加法器和先行进位的四位并行加法器,提升学生对传统逻辑电路设计、仿真和调试的能力。实验过程中,学生需要自定义逻辑门和触发器,避免直接使用Logisim的预置元件。实验还要求将先行进位的四位并行加法器封装为私有库元件,以备后续实验使用。"

在本次实验中,首先需要理解二进制加法器的基本概念。二进制加法器是数字逻辑电路中的基本组成部分,用于执行二进制数的加法运算。实验中涉及到的五种加法器分别为:

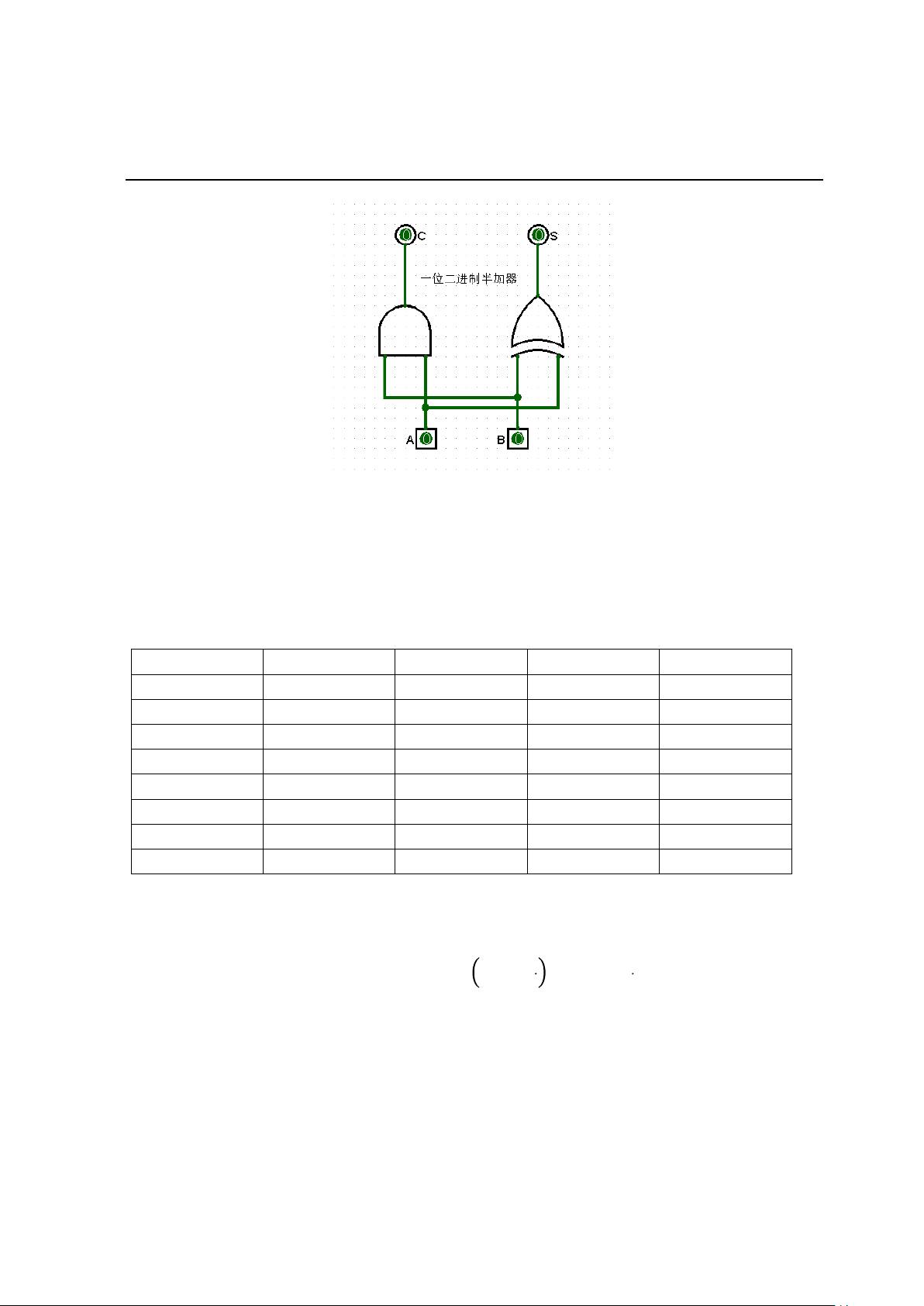

1. 一位二进制半加器:半加器是最简单的二进制加法器,它只有两个输入A和B,分别代表被加数和加数,以及两个输出S和C。S表示本位的和,C表示向高位的进位。半加器不考虑来自低位的进位,因此只处理两位二进制数的加法。

2. 一位二进制全加器:全加器比半加器多了一个输入Ci,代表来自低位的进位,使得全加器可以处理三位二进制数的加法。全加器有三个输入A、B和Ci,两个输出S和Co,S是本位和,Co是向高位的进位。

3. 串行进位的四位二进制并行加法器:由四个一位全加器串联组成,用于计算四位二进制数的加法。每个全加器的进位输出连接到下一个全加器的进位输入,最后一个全加器的进位输出C4作为整个加法器的高位进位。

4. 先行进位的四位二进制并行加法器:采用了超前进位的概念,通过预先计算高位的进位,加快了加法运算的速度。同样也是四个全加器组成,但通过优化设计,减少了进位延迟。

5. 先行进位的四位并行加法器的封装:设计完成后,学生需要将这个组件封装成一个独立的逻辑元件,创建私有库,以便于在后续实验中复用。封装的过程包括绘制逻辑符号,定义输入输出端口,并确保封装后的元件在Logisim中能正确模拟运算。

通过这些实验,学生不仅能够掌握基本的逻辑门电路(如与门、或门、非门、异或门等)和触发器(如D触发器、JK触发器等)的使用,还能深入了解二进制加法运算的逻辑过程,同时锻炼逻辑思维能力和软件应用技能,尤其是使用Logisim进行电路设计和仿真的能力。在实验过程中,不断地调整和验证电路,有助于提高问题解决和分析能力,为更复杂的数字系统设计打下坚实基础。

2019-11-21 上传

2020-04-22 上传

2021-10-11 上传

2023-07-31 上传

2023-03-30 上传

2023-11-12 上传

2023-12-22 上传

2023-08-15 上传

2023-09-03 上传

代码深渊漫步者

- 粉丝: 21

- 资源: 320

最新资源

- 磁性吸附笔筒设计创新,行业文档精选

- Java Swing实现的俄罗斯方块游戏代码分享

- 骨折生长的二维与三维模型比较分析

- 水彩花卉与羽毛无缝背景矢量素材

- 设计一种高效的袋料分离装置

- 探索4.20图包.zip的奥秘

- RabbitMQ 3.7.x延时消息交换插件安装与操作指南

- 解决NLTK下载停用词失败的问题

- 多系统平台的并行处理技术研究

- Jekyll项目实战:网页设计作业的入门练习

- discord.js v13按钮分页包实现教程与应用

- SpringBoot与Uniapp结合开发短视频APP实战教程

- Tensorflow学习笔记深度解析:人工智能实践指南

- 无服务器部署管理器:防止错误部署AWS帐户

- 医疗图标矢量素材合集:扁平风格16图标(PNG/EPS/PSD)

- 人工智能基础课程汇报PPT模板下载