Vivado教程:从代码到硬件——生成bit文件流程

需积分: 0 187 浏览量

更新于2024-08-05

收藏 456KB PDF 举报

"这篇内容主要介绍了在数字逻辑与部件设计实验中,如何将代码转换为电路并生成bit文件的步骤,以及硬件描述语言SystemVerilog的基础语法。"

在数字逻辑与部件设计实验中,开发流程至关重要,特别是对于将代码转换为可运行在硬件上的bit文件。以下是将代码转化为电路并生成bit文件的具体步骤:

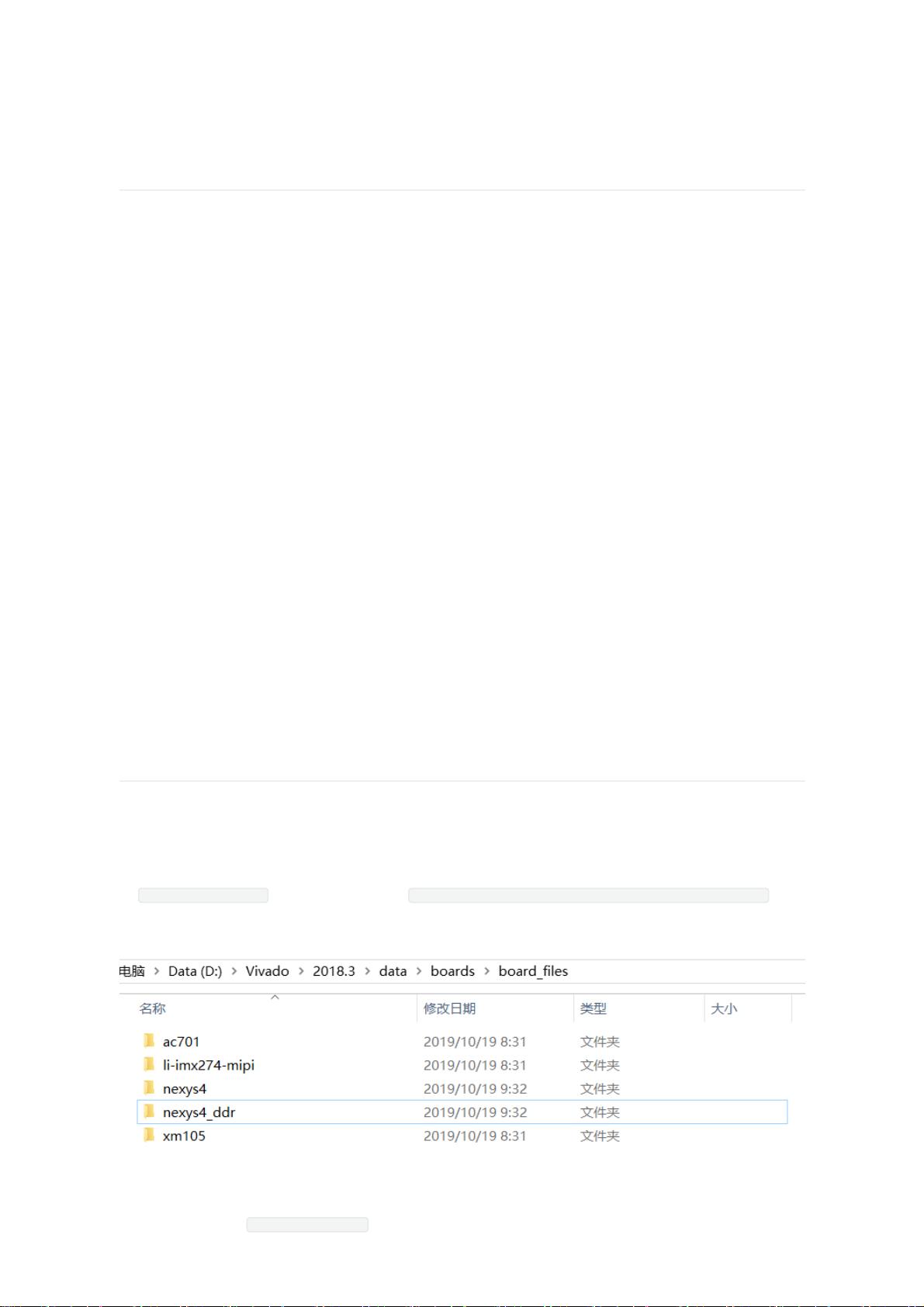

1. **添加实验板信息**:首先,需要在Vivado的安装目录下添加实验板的配置信息。这通常涉及将board_files.zip解压缩到特定的目录,确保Vivado能够识别实验板。

2. **新建项目**:在Vivado环境中创建新项目,选择项目路径,然后选择RTL Project。在DefaultPart界面,通过Boards选项选择对应的实验板,如Nexys4DDR,并按照向导完成项目创建。

3. **运行tcl脚本添加源文件**:利用tcl脚本(如sources.tcl)可以自动化地将所有必要的源文件添加到项目中。脚本会指定顶层文件和设置仿真文件,确保所有组件都被正确引用。

硬件描述语言(HDL)是实现数字逻辑设计的关键工具。这里特别提到了SystemVerilog,一种强大的硬件描述语言:

- **二进制位变量声明**:SystemVerilog允许声明不同宽度的二进制位变量,以表示各种数字逻辑信号。

- **常量**:可以声明常量以定义固定的数值,增强代码的可读性和复用性。

- **assign语句**:用于连接电路,将一个信号的值赋给另一个信号,类似于软件中的赋值操作。

- **模块与元件**:模块是SystemVerilog的基本构建块,代表硬件电路的一部分。元件例化则是将模块实例化到电路中,实现功能模块间的连接。

- **运算符**:SystemVerilog支持丰富的运算符,包括算术、逻辑和比较运算符,使得逻辑表达式编写更为简洁。

生成bit文件的最后几个步骤包括开启多线程以加速编译(如果需要),执行综合、布局布线等流程,最终生成bitstream。生成的bit文件是硬件配置文件,可以被加载到FPGA(Field Programmable Gate Array)中,使FPGA执行相应的逻辑功能。

一旦bit文件生成,可以通过JTAG或SPI等接口将其上载到实验板,从而使硬件执行已设计的逻辑。在这个过程中,理解硬件描述语言和Vivado工具的使用是至关重要的,因为它们是实现从软件代码到硬件实现的关键桥梁。

文润观书

- 粉丝: 31

- 资源: 317

最新资源

- 毕业设计&课设--扶贫助农管理系统-毕业设计.zip

- 3d-nii-visualizer:使用VTK和Qt5的NIfTI(nii.gz)3D可视化工具

- GoogleIntegratedSystemConky:适用于Linux用户的带有Google Keep,Google日历,系统信息和Lua时钟的Conky配置

- Qaccidentmap

- Excel模板企业付款申请单支付申请单模板.zip

- snake-test

- 毕业设计&课设--东北大学本科毕业设计 论文latex模板 .zip

- custom_timechart

- weather_app:天气应用程序,它使用openweathermap.org中的数据提供基于城市或美国邮政编码的天气状况和天气预报

- Reviewable:支持可审核

- 毕业设计&课设--大四毕业设计做的基于树莓派的人脸识别系统(调用百度云api).zip

- takimApp

- Excel模板创意进销存.zip

- bemaker:WELL项目建设者

- 编码教程:来自我的Twitch流和YouTube视频的一系列编码教程

- Operating-Systems-One:操作系统

已收录资源合集

已收录资源合集