使用SVAUnit进行形式验证

需积分: 5 124 浏览量

更新于2024-06-20

2

收藏 13.15MB PPTX 举报

"SVAUnit and Assertions for Formal是关于使用SystemVerilog断言(SVA)进行形式验证的教程,特别提到了SVAUnit这一工具。SVAUnit是一种用于编写和组织SystemVerilog断言的框架,它使得在验证过程中利用断言更加方便和结构化。该教程由Andra Radu和Ionuț Ciocîrlan主讲,涵盖了SystemVerilog断言的基础知识,包括规划、实现和使用SVAUnit进行验证。"

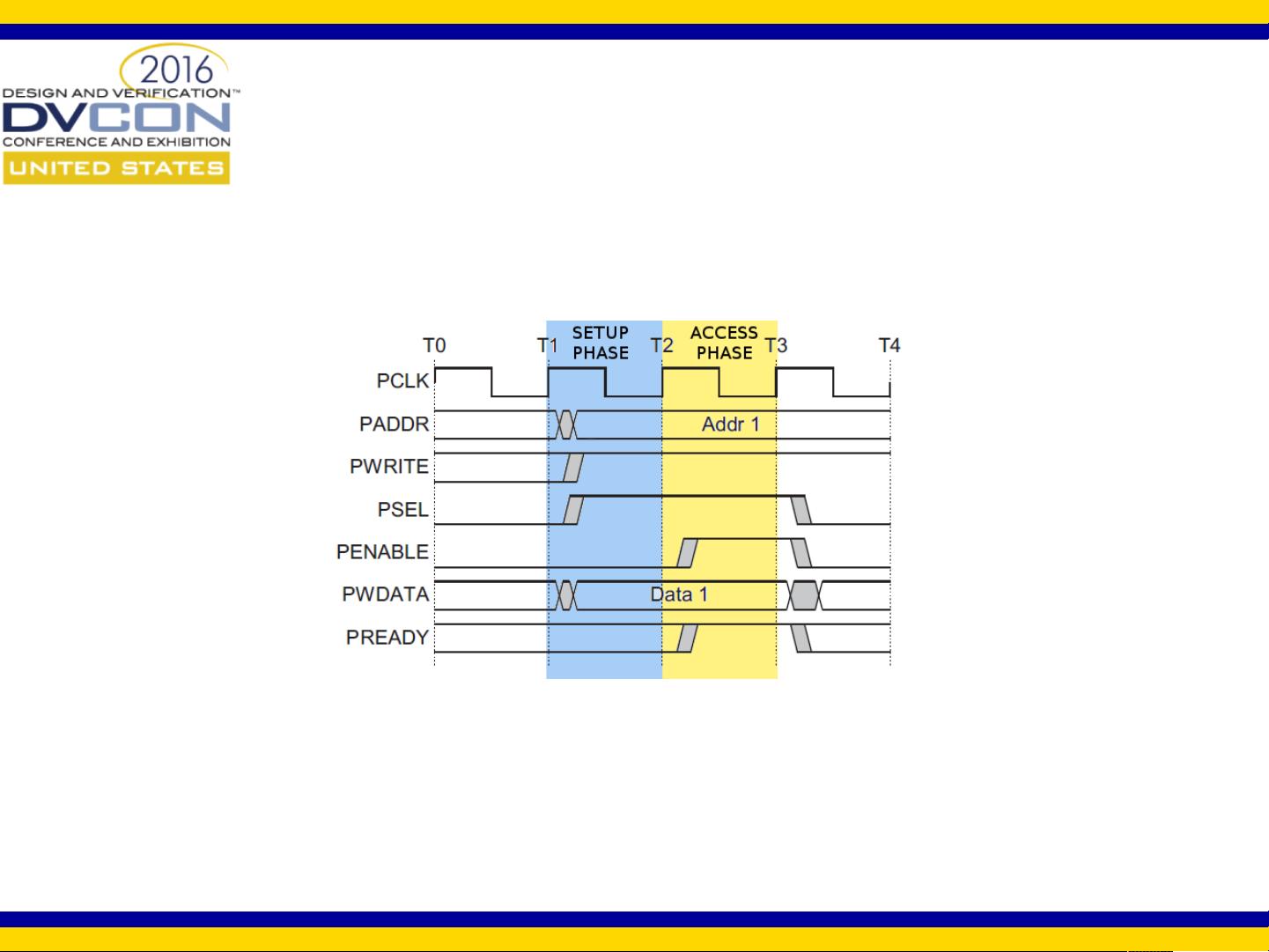

在深入探讨SVAUnit和形式验证之前,我们首先需要理解什么是SystemVerilog断言(SVA)。断言在硬件验证中扮演着关键角色,它允许设计者定义和检查期望的行为,以确保系统在特定条件下的正确性。SystemVerilog提供了两种类型的断言:即时断言和并发断言。

即时断言在时钟周期的特定时刻执行,如`assert`语句,它会在给定的表达式不满足时立即触发错误。例如,`assert(a|->b)`表示如果a为真,则b必须在接下来的一个或多个时钟周期内变为真,否则将触发错误消息。

并发断言则是在整个时间跨度内持续检查的条件,它们通常与时钟边缘或其他时间事件相关联。如`property`关键字定义的断言,`property req_to_rise_p; @(posedge clk) $rose(req) |-> ##[1:3] $rose(ack); endproperty`表示当请求信号`req`上升沿之后,响应信号`ack`必须在1到3个时钟周期内上升,否则也会报告错误。

SVAUnit则是一个专为形式验证设计的框架,它扩展了SystemVerilog断言的概念,提供了测试套件的结构,使验证工作更易于管理和调试。使用SVAUnit,可以定义断言测试用例,这些用例可以像传统的UVM测试用例一样运行,并且可以集成到现有的验证环境中。例如,通过使用`ASSERT_LABEL: assertproperty(req_to_rise_p)`,可以指定一个断言标签并在失败时调用`uvm_error`宏来记录错误信息。

通过SVAUnit,开发者能够更有效地组织和管理形式验证中的断言,提高验证覆盖率和效率。此外,SVAUnit还支持对断言进行参数化、分组和调试,从而简化复杂设计的验证流程。结合SVA的即时和并发断言,SVAUnit成为了一种强大的工具,帮助工程师在形式验证中实现更高效、更全面的验证策略。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-05-28 上传

2015-03-21 上传

2019-11-19 上传

2018-12-26 上传

2017-10-01 上传

2014-05-26 上传

babydream520

- 粉丝: 65

- 资源: 25

最新资源

- todoey_flutter:创建一个简单的待办事项清单

- pracwebdev-assignment7

- AbpCodeGeneration:基于Abp构建的代码生成器,避免了基础代码的编写

- prak-PBO

- AIOrqlite-0.1.2-py3-none-any.whl.zip

- FFEncoder:一个PowerShell脚本,使用ffmpeg使编码工作流更容易

- toDO

- dev-fest-2019:在Kotlin中显示了如何使用动态模块,MVVM,Room,DI,应用程序捆绑和内部应用程序共享(PlayStore)的应用程序)

- 雅虎销售页面模板

- python-package-boilerplate:Python包cookiecutter样板

- Fullstack-Weatherly:使用Reactjs,Expressjs和Typescript制作的全栈天气应用程序

- python-scripts:我制作的Python脚本

- email-to-name:根据常见模式从电子邮件地址生成名称

- self-driving-car:包含自动驾驶汽车算法

- 随机森林

- tiempo-muerto