EDA数字时钟设计与实现

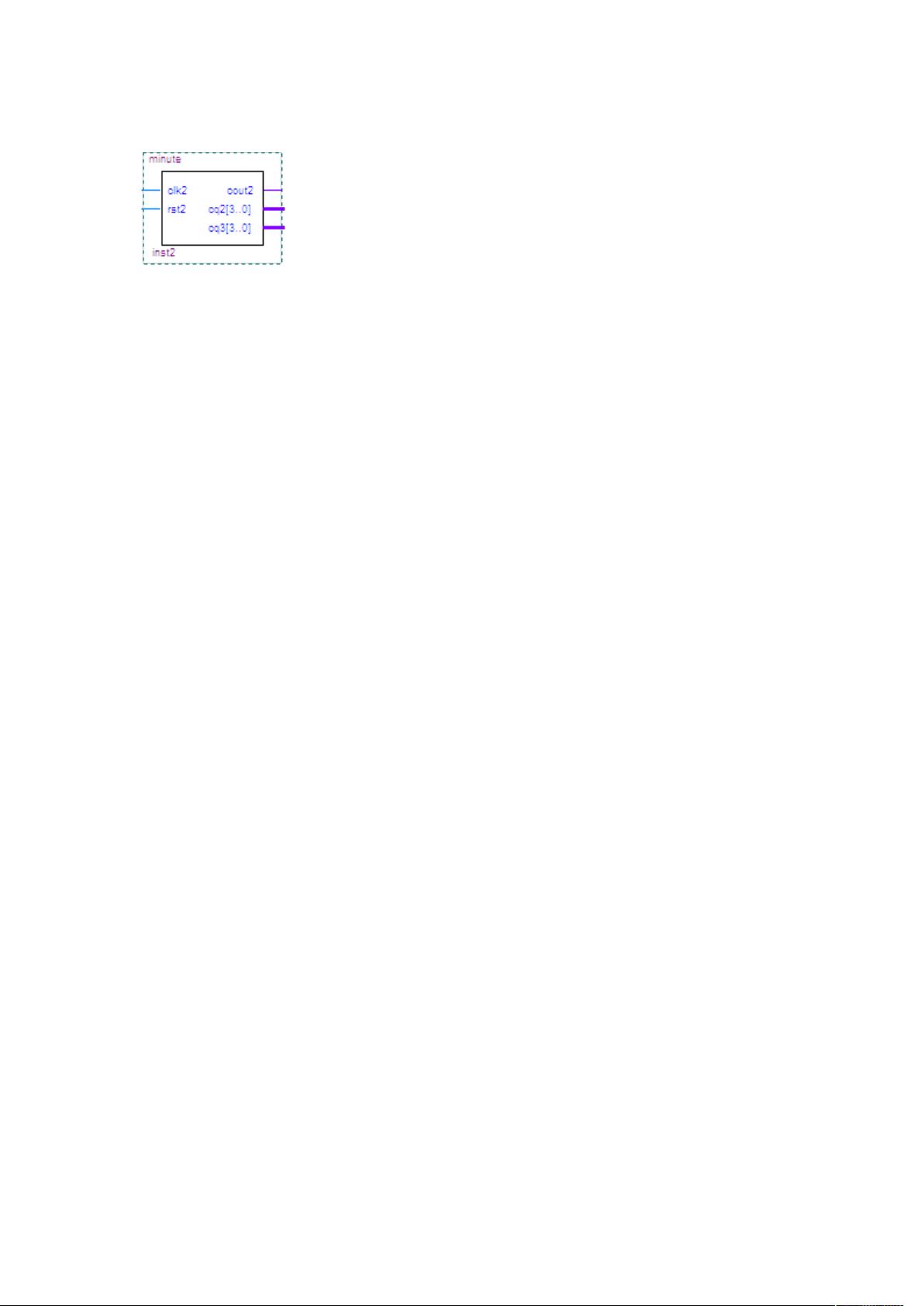

"EDA小王子使用QuartusII软件和EDA实验箱,设计了一个多功能数字时钟,包括小时、分钟的显示,12/24小时制切换,以及调节键和功能键。系统核心是六十进制计数器,用以实现时间的精确计时。在设计中,秒计时部分采用了一个60进制计数器,由clk1时钟信号驱动,rst1作为复位信号,cout1输出进位,cq0和cq1分别输出十位和个位的秒数。"

在EDA(电子设计自动化)领域,数字时钟的设计是一个典型的项目,它涉及到数字逻辑和时序电路的概念。本实验的主要目的是让学生熟悉复杂数字电路系统的设计流程,并实际操作设计一个具备多种功能的数字时钟。实验内容包括:

1. **六十进制计数器**:计数器是数字系统的基础组件,用于计数特定数量的时钟周期。在这个设计中,六十进制计数器被用来表示秒,当秒数达到60时会进行进位。

```vhdl

entity second IS

port(clk1, rst1: in std_logic;

cout1: out std_logic;

cq0, cq1: out std_logic_vector(3 downto 0));

END second;

```

在这个实体定义中,`clk1`是时钟输入,`rst1`是复位信号,`cout1`是进位输出,而`cq0`和`cq1`则是秒数的十位和个位。

2. **时序逻辑处理**:在结构化的行为架构(`ARCHITECTURE behave OF second`)中,使用了一个进程来处理时序逻辑。这个进程在时钟边沿触发,当`rst1`为高时,计数器清零。在时钟上升沿,如果当前秒数达到9并且分钟的十位数达到5,`cout1`被设置为高,表示秒进位。秒数和分钟十位数分别根据条件更新,确保了六十进制的计数行为。

3. **接口设计**:设计中还涉及到了接口设计,`cq0`和`cq1`输出的秒数是通过4位二进制表示的,这允许将数字信号转换为显示器可读的形式。

4. **功能扩展**:除了秒计时,这个数字时钟还需要实现分钟计时,以及小时、计时模式(12/24小时制)、调节等功能,这些可能通过额外的六十进制计数器和状态机来实现,通过功能键切换不同的工作模式。

5. **实验评价**:实验成绩很高,表明设计成功并有效实现了预期功能。学生通过这样的实验,不仅掌握了数字系统设计的基本技能,还锻炼了问题解决和创新思维。

这个实验涵盖了数字逻辑、时序电路、状态机、接口设计等多个关键知识点,是EDA学习中的一个重要实践环节。

2010-01-17 上传

2007-11-16 上传

2011-05-11 上传

2012-06-12 上传

2009-06-14 上传

点击了解资源详情

2023-05-23 上传

2023-12-09 上传

yangkaibvv1

- 粉丝: 0

- 资源: 1

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码