西北工大Verilog状态机设计与FPGA实战教程

需积分: 15 155 浏览量

更新于2024-08-04

1

收藏 1.9MB DOCX 举报

本次实验旨在通过西北工业大学的数字逻辑与Verilog设计课程,让学生深入理解并掌握Verilog语言在状态机设计中的应用以及在FPGA上的实际实现过程。实验四的重点在于以下几个方面:

1. Verilog语言基础:实验首先强调了掌握可综合的Verilog语言,这是一种硬件描述语言,用于描述数字电路的行为。学生需要熟练编写状态机模块,确保代码能被编译器理解和转换成可执行的电路结构。

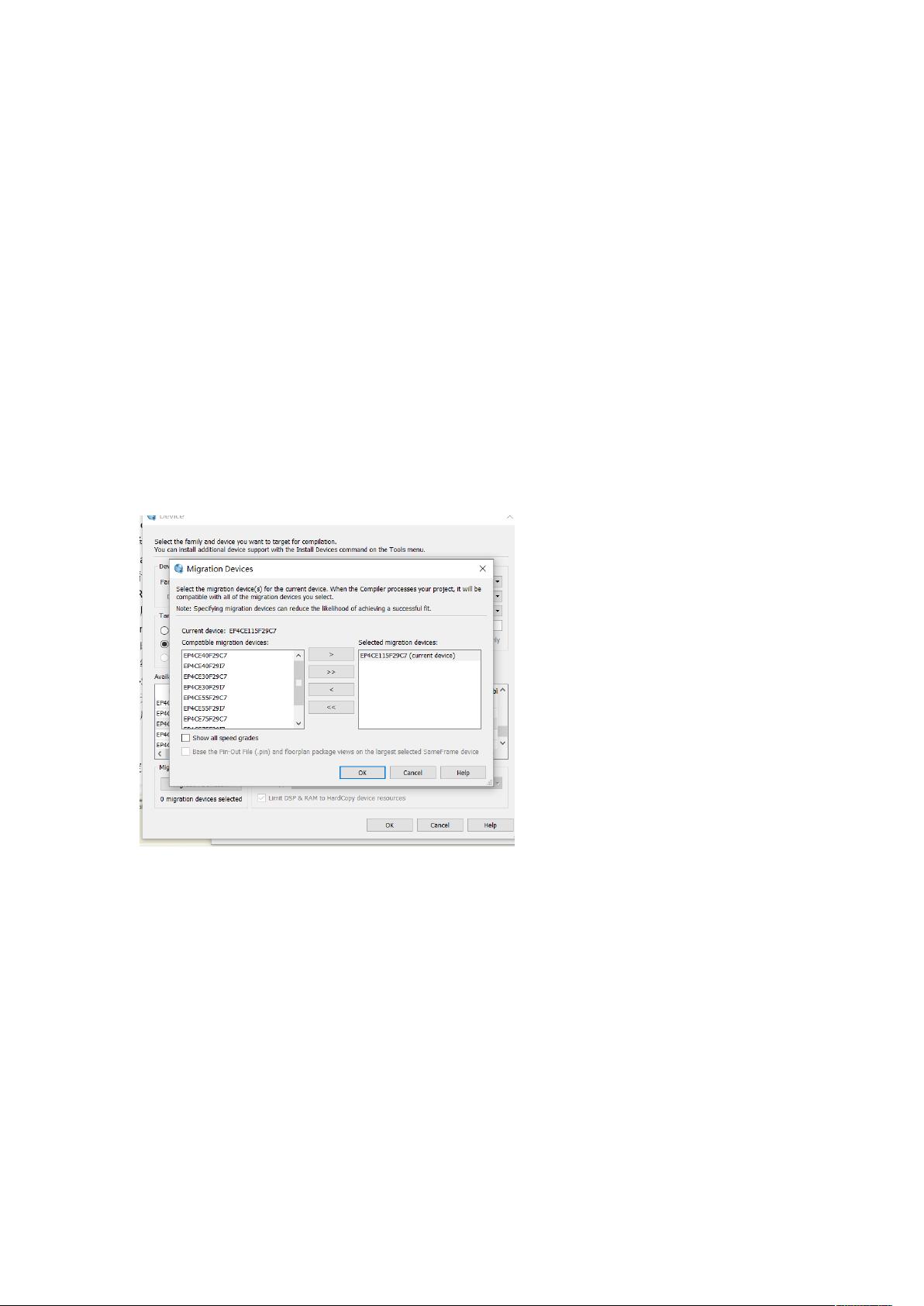

2. Quartus II软件操作:使用Quartus II作为主要的设计和开发工具,包括创建新项目、添加源文件、编译和调试。学生需了解如何正确设置工程参数,如选择合适的FPGA型号(Cyclone IV EP4CE115F29C7),并确保模块名与工程名的一致性。

3. 跑马灯设计与FPGA实现:通过实例演示,学生将设计一个简单的跑马灯,该设计包含一个计数器和状态机。他们需要编写Verilog代码实现灯的亮灭模式变化,根据计数器的值来决定输出的二进制代码。这个过程涉及了时序逻辑的设计和测试验证。

4. 电路结构与管脚绑定:利用RTL viewer工具检查电路结构是否符合预期,确保设计的正确性。同时,通过pin planner功能,将设计的输入输出接口与开发板的物理引脚一一对应,这是硬件连接的关键步骤。

5. 综合与下载:完成所有设计和配置后,进行全编译生成可下载文件(.sof),以便将设计加载到FPGA上进行实际测试和验证。这一步骤涉及到编译错误的处理和调试,确保最终设计能够成功运行。

通过这个实验,学生不仅提升了Verilog编程技能,还学会了如何将设计概念转化为实际的硬件实现,这对于理解和应用现代集成电路技术至关重要。实验结束后,学生应该能够独立完成类似的状态机设计,并能对设计结果进行有效的分析和优化。

2020-12-16 上传

2020-12-15 上传

2020-12-16 上传

2020-12-15 上传

2024-05-16 上传

2024-05-16 上传

2024-05-16 上传

2021-11-20 上传

2022-11-13 上传

CoderGirl∞

- 粉丝: 37

- 资源: 8

最新资源

- rabbitmq:rabbitmq实战,多个服务之间使用消息队列

- wdi_8_js_lab_hacker_news_frontend

- multischemase:Multischemase是用于对数据库进行版本控制的工具。 易于使用且易于设置。 完全在节点中,非常轻

- 电信设备-基于信息泄露容错智能卡的三方口令认证与密钥协商协议.zip

- 基于HTML实现的漂亮的设计行业作品案例单页跳转(含HTML源代码+使用说明+毕业设计).zip

- 易语言-易语言汇编版ByteBuffer

- 蓝色雪花特效表白网站模板

- 测试

- gstoica27.github.io

- react-beforeunload:React组件和挂钩,侦听beforeunload窗口事件

- korean_translator

- i微链-crx插件

- 电信设备-发送功率控制系统及方法、以及相关基站和移动通信终端.zip

- jenkins-sessions

- n-queens:一个使用非常简单的遗传算法解决 N-Queens 问题的 Javascript 程序

- imdone-core:基于文本的看板处理器