FPGA实现:奇偶数分频与半整数分频设计探索

下载需积分: 10 | DOC格式 | 3.17MB |

更新于2024-10-19

| 63 浏览量 | 举报

"基于FPGA的分频器设计与实现,包括偶数分频和奇数分频,重点探讨了半整数分频和等占空比的奇数分频方法,采用VHDL硬件描述语言进行编程,并通过QUARTUS||4.0进行仿真验证,最终在FPGA芯片上实现。"

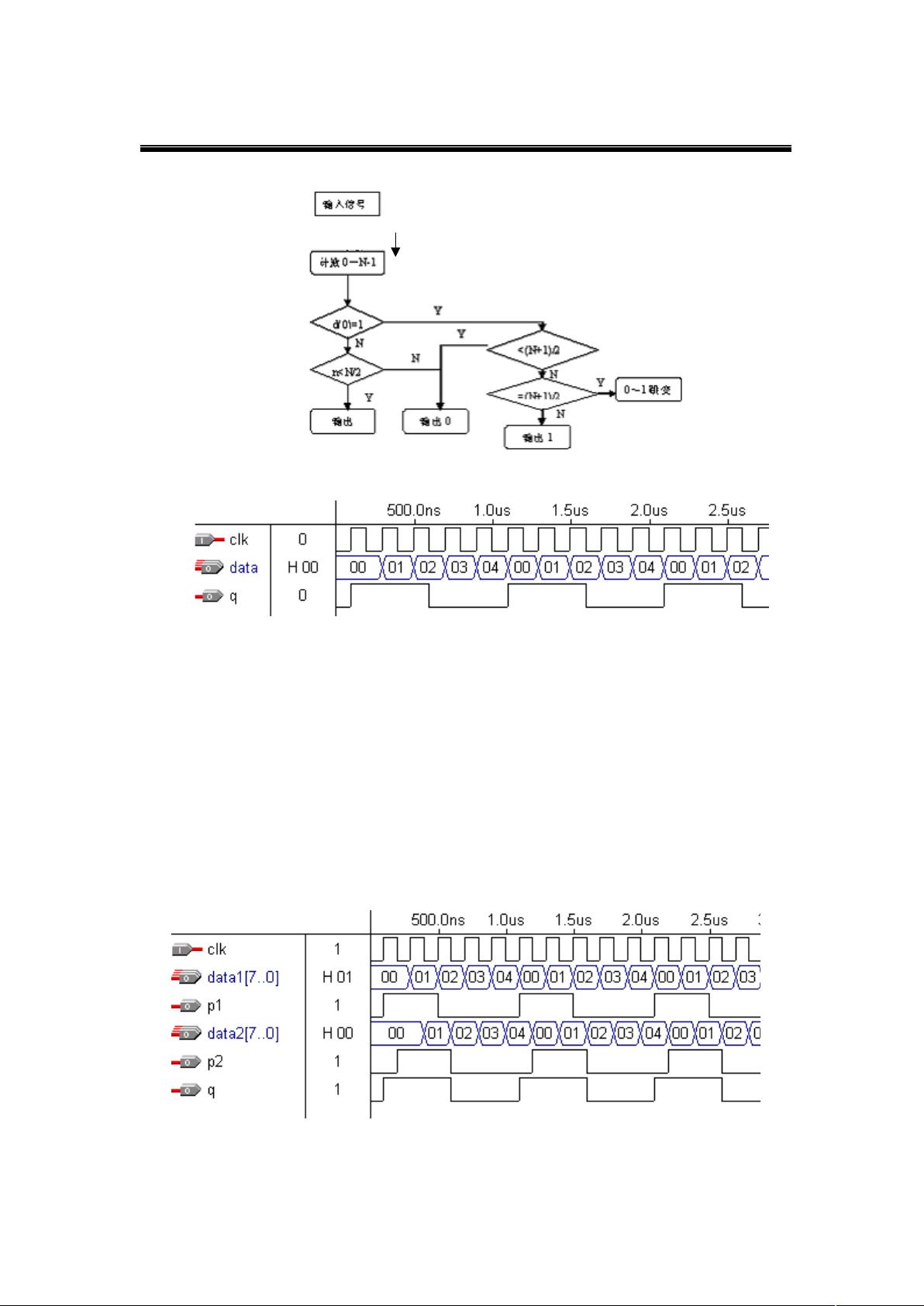

在数字系统设计中,分频器扮演着至关重要的角色,它可以将输入信号的频率按特定的比例降低,以满足不同应用的需求。基于FPGA的分频器设计提供了一种灵活且可重构的方法来实现各种分频功能。本文着重讨论了如何在FPGA上实现偶数分频和奇数分频,尤其是在处理奇数分频时,提出了新的设计方案。

通常,奇数分频实现起来较为复杂,因为其输出脉冲的占空比难以保持50%。传统的解决方案是先将输入频率翻倍,然后进行偶数分频,但这会限制设计的最高工作频率并增加硬件资源的消耗。针对这一问题,文章提出了一种创新的FPGA设计,可以在不进行预倍频的情况下实现等占空比的奇数分频,有效地提升了频率资源的利用率,同时降低了设计复杂度。

设计中采用了VHDL语言,这是一种广泛使用的硬件描述语言,允许开发者以结构化的方式描述数字系统的逻辑功能。通过VHDL编程,设计者可以清晰地定义分频器的行为,然后使用像QUARTUS||4.0这样的EDA工具进行仿真验证,确保设计的正确性。最后,经过验证的设计会被综合并下载到FPGA芯片上,实现在实际硬件上的运行。

文章的技术要求包括支持28-0.5范围内的整数和半整数分频,并能对任意分频实现等占空比或非等占空比的输出。这些特性使得设计的分频器具有广泛的适用性,能够适应不同的应用场景。技术特点是利用FPGA的灵活性,避免了传统方法中的预倍频步骤,降低了对硬件资源的需求,提升了系统性能。

这篇文章提供了关于FPGA实现分频器的深入见解,特别是在奇数分频和等占空比控制方面的独特解决方案,对于理解和设计高性能的FPGA分频器具有重要的参考价值。通过这种方式,开发者能够优化他们的数字系统设计,更高效地利用FPGA资源,同时满足复杂的分频需求。

相关推荐

东方狄龙

- 粉丝: 3

最新资源

- ITween插件实用教程:路径运动与应用案例

- React三纤维动态渐变背景应用程序开发指南

- 使用Office组件实现WinForm下Word文档合并功能

- RS232串口驱动:Z-TEK转接头兼容性验证

- 昆仑通态MCGS西门子CP443-1以太网驱动详解

- 同步流密码实验研究报告与实现分析

- Android高级应用开发教程与实践案例解析

- 深入解读ISO-26262汽车电子功能安全国标版

- Udemy Rails课程实践:开发财务跟踪器应用

- BIG-IP LTM配置详解及虚拟服务器管理手册

- BB FlashBack Pro 2.7.6软件深度体验分享

- Java版Google Map Api调用样例程序演示

- 探索设计工具与材料弹性特性:模量与泊松比

- JAGS-PHP:一款PHP实现的Gemini协议服务器

- 自定义线性布局WidgetDemo简易教程

- 奥迪A5双门轿跑SolidWorks模型下载