TLC1549C, TLC1549I, TLC1549M

10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL

SLAS059C – DECEMBER 1992 – REVISED MARCH 1995

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

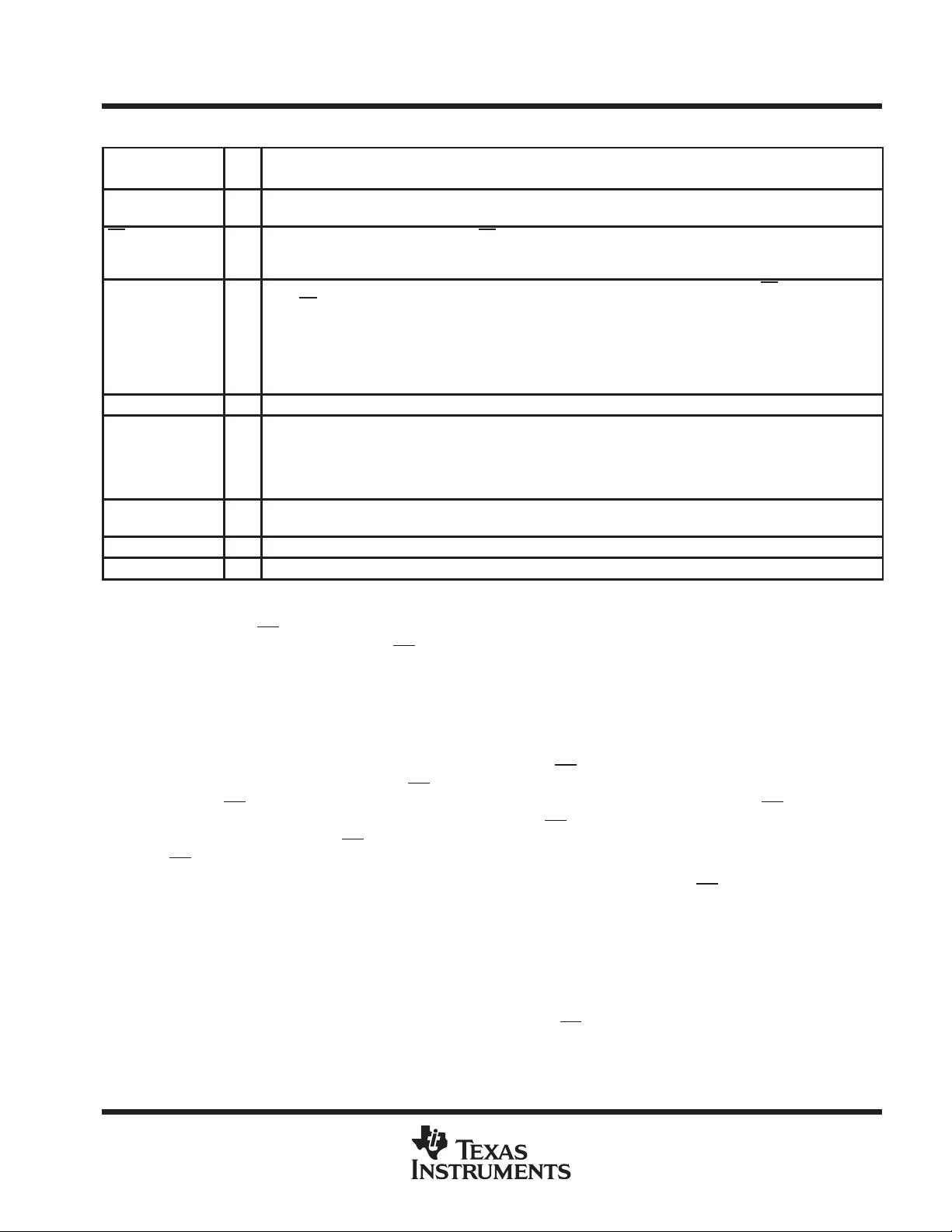

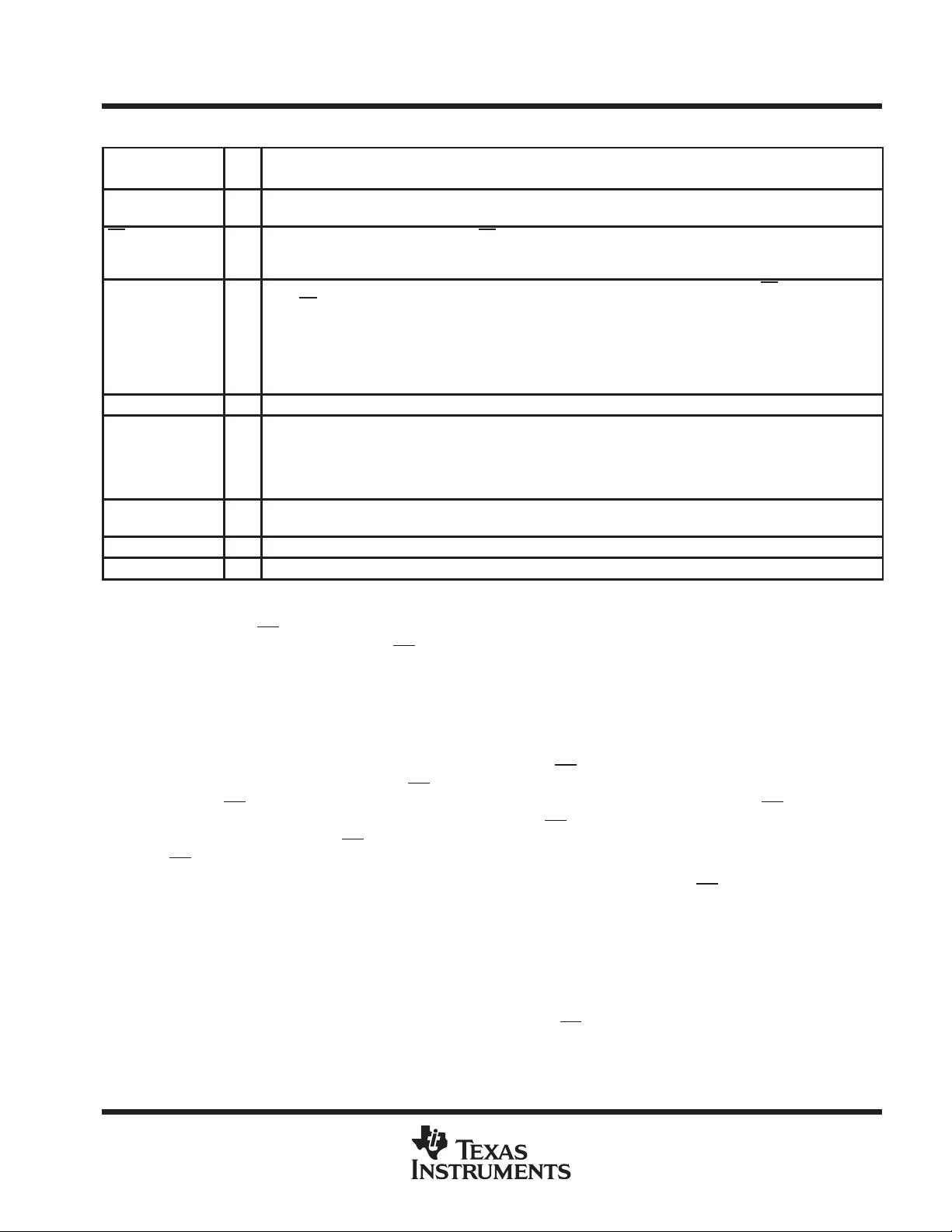

Terminal Functions

TERMINAL

NAME NO.

ANALOG IN 2 I Analog signal input. The driving source impedance should be ≤ 1 kΩ. The external driving source to ANALOG IN

should have a current capability ≥ 10 mA.

CS 5 I Chip select. A high-to-low transition on CS resets the internal counters and controls and enables DATA OUT and

I/O CLOCK within a maximum of a setup time plus two falling edges of the internal system clock. A low-to-high

transition disables I/O CLOCK within a setup time plus two falling edges of the internal system clock.

DATA OUT 6 O This 3-state serial output for the A/D conversion result is in the high-impedance state when CS is high and active

when CS

is low. With a valid chip select, DATA OUT is removed from the high-impedance state and is driven to

the logic level corresponding to the MSB value of the previous conversion result. The next falling edge of I/O

CLOCK drives DATAOUT to the logic level corresponding to the next most significant bit, and the remaining bits

are shifted out in order with the LSB appearing on the ninth falling edge of I/O CLOCK. On the tenth falling edge

of I/O CLOCK, DATA OUT is driven to a low logic level so that serial interface data transfers of more than ten clocks

produce zeroes as the unused LSBs.

GND 4 The ground return for internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.

I/O CLOCK 7 I Input/output clock. I/O CLOCK receives the serial I/O CLOCK input and performs the following three functions:

1) On the third falling edge of I/O CLOCK, the analog input voltage begins charging the capacitor array and

continues to do so until the tenth falling edge of I/O CLOCK.

2) It shifts the nine remaining bits of the previous conversion data out on DATA OUT.

3) It transfers control of the conversion to the internal state controller on the falling edge of the tenth clock.

REF+ 1 I The upper reference voltage value (nominally V

CC

) is applied to REF+. The maximum input voltage range is

determined by the difference between the voltage applied to REF+ and the voltage applied to REF–.

REF– 3 I The lower reference voltage value (nominally ground) is applied to REF –.

V

CC

8 Positive supply voltage

detailed description

With chip select (CS) inactive (high), I/O CLOCK is initially disabled and DATA OUT is in the high impedance

state. When the serial interface takes CS

active (low), the conversion sequence begins with the enabling of I/O

CLOCK and the removal of DATA OUT from the high-impedance state. The serial interface then provides the

I/O CLOCK sequence to I/O CLOCK and receives the previous conversion result from DATA OUT. I/O CLOCK

receives an input sequence that is between 10 and 16 clocks long from the host serial interface. The first ten

I/O clocks provide the control timing for sampling the analog input.

There are six basic serial interface timing modes that can be used with the TLC1549. These modes are

determined by the speed of I/O CLOCK and the operation of CS

as shown in Table 1. These modes are (1) a

fast mode with a 10-clock transfer and CS

inactive (high) between transfers, (2) a fast mode with a 10-clock

transfer and CS

active (low) continuously, (3) a fast mode with an 11- to 16-clock transfer and CS inactive (high)

between transfers, (4) a fast mode with a 16-bit transfer and CS

active (low) continuously, (5) a slow mode with

an 11- to 16-clock transfer and CS

inactive (high) between transfers, and (6) a slow mode with a 16-clock transfer

and CS

active (low) continuously.

The MSB of the previous conversion appears on DATA OUT on the falling edge of CS

in mode 1, mode 3, and

mode 5, within 21 µs from the falling edge of the tenth I/O CLOCK in mode 2 and mode 4, and following the

sixteenth clock falling edge in mode 6. The remaining nine bits are shifted out on the next nine falling edges of

I/O CLOCK. Ten bits of data are transmitted to the host serial interface through DATA OUT. The number of serial

clock pulses used also depends on the mode of operation, but a minimum of ten clock pulses is required for

conversion to begin. On the tenth clock falling edge, the internal logic takes DATA OUT low to ensure that the

remaining bit values are zero if the I/O CLOCK transfer is more than ten clocks long.

Table 1 lists the operational modes with respect to the state of CS

, the number of I/O serial transfer clocks that

can be used, and the timing on which the MSB of the previous conversion appears at the output.