FPGA实现的内插滤波器与定时误差检测设计

123 浏览量

更新于2024-08-30

1

收藏 243KB PDF 举报

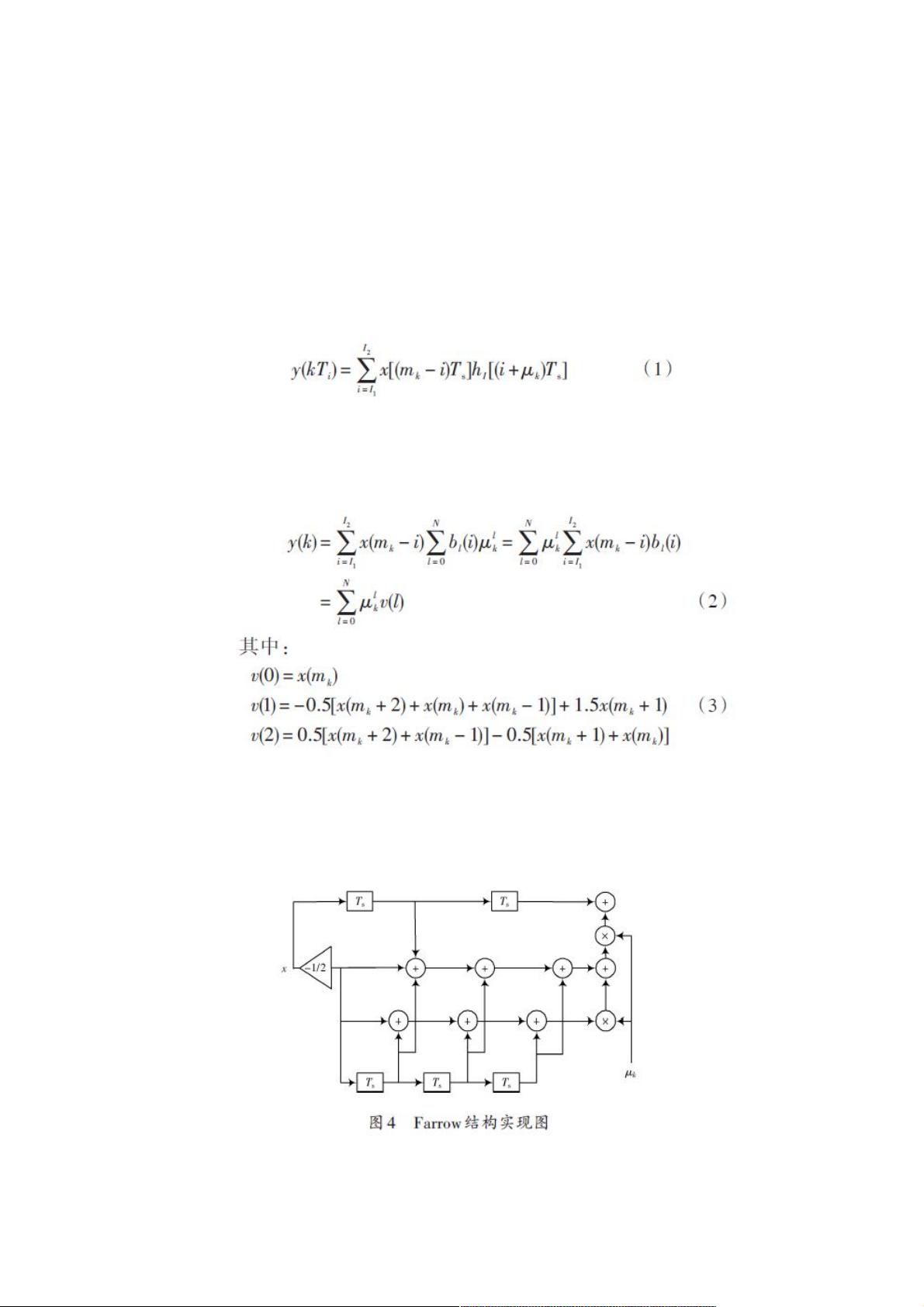

"本文主要介绍了基于FPGA的通用位同步器设计的第二部分,重点关注内插滤波器和定时误差检测模块的详细设计。内插滤波器采用Farrow结构,利用4点分段抛物线多项式实现,减少了硬件资源的使用。定时误差检测则运用GA-TED算法,每个码元周期输出一个误差信号,实现高效且低复杂度的位同步。"

在数字通信系统中,位同步是关键环节,确保接收端正确地对齐发送端的数据位流。本文阐述的基于FPGA(Field-Programmable Gate Array)的通用位同步器设计方案,主要探讨了两个核心模块的设计:内插滤波器和定时误差检测器。

内插滤波器的设计目标是根据插值参数实时计算判决点的内插值。这里采用了一种称为Farrow结构的内插滤波器,其基于4点分段抛物线多项式,能有效简化计算并减少硬件资源的需求。通过将原始的计算公式转换为拉格朗日多项式,该滤波器由移位器、触发器、相加器和乘法器组成。移位器用于执行除以2的运算,触发器存储中间结果,相加器进行数值的组合,而乘法器则进行必要的乘法运算。这种设计方法显著减少了乘法器和相加器的数量,从而降低了FPGA的逻辑资源消耗。

接下来,文章提到了定时误差检测模块,它采用了独立于载波相位偏差的GA-TED(Gardner-Ashkin-Teller Error Detection)算法。GA-TED算法的优点在于每个符号周期只需要两次插值,可以实时产生误差信号,指导位定时的调整。在FPGA实现时,为了优化计算效率,用符号位代替实际数值来计算误差信息,减少了乘法操作。根据符号位的比较,可以判断误差的方向,并输出相应的误差信号。

这个基于FPGA的位同步器设计方案通过巧妙的硬件结构和算法选择,实现了高效、节省资源的位同步功能。内插滤波器的Farrow结构与定时误差检测的GA-TED算法相结合,确保了在数字通信系统中准确地捕获和跟踪发送端的位定时,从而提高通信系统的整体性能。

2012-12-26 上传

2023-05-25 上传

2023-05-16 上传

2023-05-27 上传

2023-07-09 上传

2023-05-23 上传

2023-04-27 上传

weixin_38719643

- 粉丝: 7

- 资源: 941

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦